# **UMM AL-QURA UNIVERSITY**

College of Computer and Information Systems

**Computer Engineering Department**

14031201-4

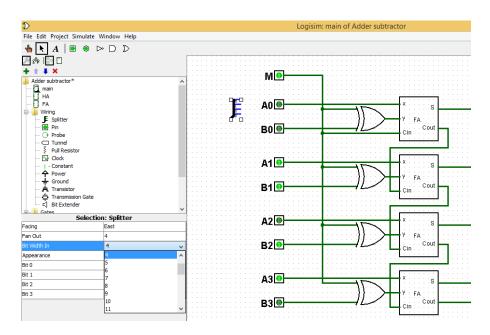

**Digital Logic Design**

Lab Manual

| Student Name:                |        |  |

|------------------------------|--------|--|

| Student ID:                  |        |  |

| Section:                     | Group: |  |

| Session (Fall / Spring / Sum | mer)   |  |

This page is intentionally left blank

## **TABLE OF CONTENTS**

| Table of Contents                                                                                   | 2    |

|-----------------------------------------------------------------------------------------------------|------|

| Laboratory Safety Guidelines                                                                        | 3    |

| General Information                                                                                 | 5    |

| Weekly Schedule (Based on the University Calendar)                                                  | 8    |

| Week (2) – Tutorial 1: Number systems – Conversions                                                 | 9    |

| Week (3) – Tutorial 2: Number systems – Operations and Codes                                        | . 10 |

| Week (4) – Experiment 1: Introduction to Logic Gates                                                | . 11 |

| Week (5) – Tutorial 3: Implementation and simplification of Boolean functions using Boolean Algebra |      |

| Week (6) – Experiment 2: Implementation and Simplification of Boolean Functions                     | . 18 |

| Week (7) – Experiment 3: NAND and NOR Implementation                                                | 25   |

| Week (8) – Tutorial 4: Implementation and simplification of Boolean functions using K-maps.         | . 35 |

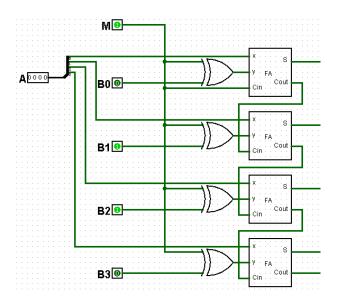

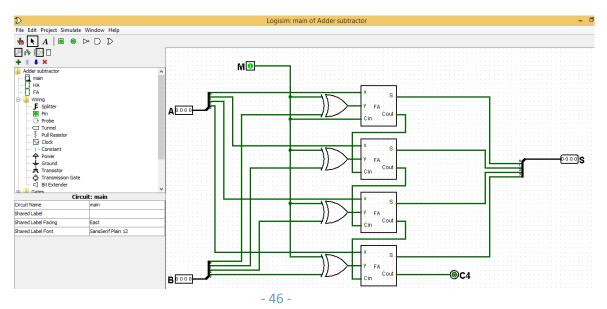

| Week (10) – Experiment 4: Combinational Logic Modules – Adders and Subtractors                      | . 36 |

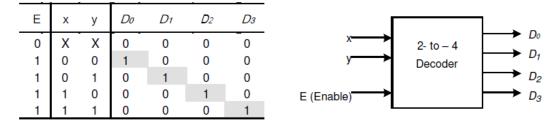

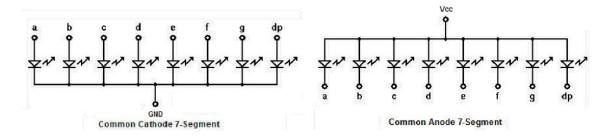

| Week (11) – Experiment 5: Combinational Logic Modules – Decoders                                    | . 48 |

| Week (12) – Experiment 6: Combinational Logic Modules – Comparators and Multiplexers                | . 54 |

| Week (13) – Experiment 7: Exam on Combinational Logic Modules – Design of an Arithmetic Circuit     |      |

| Week (14) – Tutorial 5: Sequential logic, flip flops, FSM analysis and design                       | 64   |

| Week (15) – Experiment 8: Latches, Flip Flops and Counters                                          | . 65 |

| Prepared By: | Engr. Zafar Zaheer-ul-Haque             | 2012 |

|--------------|-----------------------------------------|------|

| Revised By:  | Dr. Khaled Khayyat and Dr. Ahmed Morgan | 2016 |

| Reviewed By: |                                         |      |

| Approved By: |                                         |      |

## Umm Al-Qura University Computer Engineering Department

#### LABORATORY SAFETY GUIDELINES A. General Laboratory Safety Rules

#### 1. Personal Safety

- Be familiar with the electrical and fire hazards associated with your workplace.

- Be as careful for the safety of others as for yourself. Think before you act.

- Be tidy and systematic.

- Avoid bulky, loose or trailing clothes. Avoid long loose hair.

- No one is allowed to enter in the lab area bare foot due to increased risk of electric shock.

- Remove metal bracelets, rings or watchstraps when working in the laboratories.

- Avoid working with wet hands and clothing.

#### 2. Food, Beverages and Smoking

- Due to the increased risk of electric shock, no drinking of beverages, consumption or storage of any kind of food is allowed in the laboratory.

- Smoking is prohibited in all laboratories in all timings.

#### 3. Soldering

- No one is allowed to do soldering in any of the computer engineering laboratories except the graduation project design laboratory.

- Anyone doing soldering in the graduation project design laboratory must wear appropriate apparel, socks, gloves, covered shoes and safety goggles to prevent the possibility of severe burns resulting from the splashing or dripping of hot liquefied solder into the face and eyes or on to the exposed skin on the chest, hands, legs, and feet.

- Students who are not so properly attired for these tasks will NOT be allowed to perform any type of soldering in the graduation project design laboratory.

#### 4. Laboratory Operating Hours

- Students are never allowed to work alone in any lab area other than scheduled laboratory operating hours unless either a Lab T/A or Course Instructor is present inside that lab area.

- The laboratory operating hours for students are posted on the entrance doorway and on the notice board of computer engineering department.

#### 5. Power Supply Related Safety

- Voltages above 50-VAC or 120-VDC are always dangerous.

- Extra precautions should be considered as voltage levels are increased.

- Never make any changes to circuits or mechanical layout without first isolating the circuit by switching off and removing connections to power supplies.

#### 6. Laboratory Equipment

- Lab equipment may not be removed from the Computer Engineering lab areas without the permission of the Laboratory Supervisors.

- Laboratory bench equipment (except for some lab bench computers) must be turned off before closing down the lab area for the day.

- Never open (remove cover) of any equipment in the laboratories.

- Never "jump," disable, bypass or otherwise disengage any safety device or feature of any equipment in the laboratories.

- Laboratories shall be locked when unoccupied.

#### 7. Waste Management Safety

• Know the correct handling, storage and disposal procedures for batteries, cell, capacitors, inductors and other high energy-storage devices.

#### 8. Equipment Safety

- Before equipment is energized ensure, circuit connections and layout have been checked by a Teaching Assistant (TA) and all colleagues in your group has given their consent.

- Experiments left unattended should be isolated from the power supplies. If for a special reason, it must be left on, a barrier and a warning notice are required.

- Equipment found to be faulty in any way should be reported to the lab supervisor and taken out of service until inspected and declared safe.

#### 9. Equipment Accessories

- Use extension cords only when necessary and only on a temporary basis.

- Request new outlets if your work requires equipment in an area without an outlet.

- Discard damaged cords, cords that become hot, or cords with exposed wiring.

#### **B. Electrical and Fire Emergency Responses**

#### 1. Police, Fire or Medical Emergency

- Use the telephone located in the laboratory area and press 0-996 to notify police, fire, and ambulance for emergency help.

- Everyone present in the laboratory area shall be familiar with the locations and operation of safety and emergency equipment, including but not limited to, fire extinguishers, first aid kits, emergency power off system, fire alarm pull stations, and emergency telephones.

#### 2. Electric Shock

- When someone suffers serious electrical shock, he may be knocked unconscious.

- If the victim is still in contact with electrical current, immediately turn off the electrical power source.

- If you cannot disconnect the power source, depress the Emergency Power Off switch.

- Do not touch a victim that is still in contact with a live power source; you could be electrocuted! Have someone call for emergency medical assistance immediately. Administer first-aid, as appropriate.

#### 3. Electrical Fire

- If an electrical fire occurs, try to disconnect the electrical power source, if possible.

- If the fire is small and you are not in immediate danger; and if you have been properly trained in fighting fires, use the correct type of fire extinguisher to extinguish the fire.

- When in doubt, push in the Emergency Power Off button.

- NEVER use water to extinguish an electrical fire.

#### 4. Emergency Power Off

- Every lab is equipped with an Emergency Power off System.

- When this switch is depressed, electrical power to the lab will shut off, except for lights.

- Only authorized personnel are permitted to reset power once the Emergency Power Off system has been engaged.

#### 5. Building Evacuation in Emergency

- Everyone present in the laboratory should be familiar to emergency exits & way out plans.

- Use the nearest exit doorway from lab area closest to the stairwell to exit the building.

- Follow the Emergency Exit Signs posted in the hallways. Do not use elevators.

- Lab Teaching Assistants (T/As) or Instructor shall make sure all persons are out of the laboratory area and follow the directions posted at each doorway to the laboratory area.

The above general laboratory safety rules are designed to safeguard you and your co-workers, fellow students and colleagues and are a minimum requirement for individuals working in the computer engineering laboratories at Umm Al-Qura University, Makkah Al-Mukarramah. Specialized training and rules may apply depending on type and scope of activities involved.

## **General Information**

# 1. Introduction to the Lab:

- Each lab is a 3-hour session

- The lab objective is to introduce students to the practical world of digital system design and the various digital components. This includes how design digital circuits, how to simulates them using software packages, and how to construct them using standard Integrated Circuits (ICs) and other hardware that are readily available commercially. Students will also be familiarized with the procedure of designing, simplifying, simulating, implementing and testing many combinational and sequential circuits that explained and presented in lectures.

- Some parts of the labs do not give you step-by-step instructions on how to do them. They require you to think carefully about how you are going to do them.

- You will do the labs with the Logisim software as well as prototype boards and components that are offered to you. Logisim is a free graphical tool for designing and simulating logic circuits. You could download it from: <u>http://www.cburch.com/logisim/</u>. The website also includes some documents that help you getting started with the software.

- Every effort will be made to cover the lab materials in class before the scheduled lab period. However, if the lectures do lag behind the labs, please consult the textbook, the notes, the TA or the course instructor for any information you need.

# 2. Lab Rules:

- Be regular and disciplined: Students are expected to attend all lab sessions regularly.

- Come to the lab sessions on time. Action may be taken to late comers.

- The due date for any lab report is one week after the lab is done. Submit your lab reports on time. Any late report, for no valid reason, will not be accepted.

- Lab is yours, so help to keep it clean. Bringing foods, water or newspaper are forbidden.

- Come prepared. Read the background information and discuss the experiment with your colleagues before coming.

- Bring the Lab manual on every time you come to the laboratory.

- Do not make walking around, chatting, or noise during lab period.

- Do not change your lab group or bench without taking a permission from the Lab instructor.

- Do not do anything in a hurry. Ask the instructor if you don't understand any point or step.

- Each lab is to be demoed to the lab TA to confirm its operation. Furthermore, the TA will ask questions regarding the lab, to ensure the proper understanding of the lab materials.

- After finishing the experiment, disconnect the connection wires that you used during the experiment, and put them in the wire kit, take out all IC chips from the training kit and put them back in the IC Cabinet. Be sure to return all materials you used, to clean your table, and to inform the Lab instructor when you depart.

- The student's mark will be affected if these rules are not obeyed.

# 3. Grading :

• The Lab weights 25% of the whole course grade, the following grading scheme will be used:

| Technical Reports                                 | 5%  |

|---------------------------------------------------|-----|

| Participation and Activities                      | 5%  |

| Experiment 7: Exam on Combinational Logic Modules | 5%  |

| Final Lab Exam                                    | 10% |

- Discipline and preparedness will be taken into account when assessing the student.

- Two marks will be discarded for each unexcused absence.

- A student who has more than two unexcused absence will receive a final grade of zero.

- Students could discuss their lab experiment and results with each others. However, every student should write his/her report by himself/herself. <u>No marks</u> will be given if any cheating in the way of copying is noticed.

## 4. Requirements for Lab Reports:

- Lab reports should be submitted in a week from the date the lab is performed and should include all of the following sections:

- Cover Page: The cover page of your lab report should include the experiment name and number, your name and number, your bench order and the submission date.

- Discussion and Conclusions: In this section, you present the results you got during the lab, your observations about these results, your comments, and your conclusions.

- Questions answers: if your lab manual includes questions to be answered, you should answer all the questions completely and accurately. Some questions require you to simulate certain circuits. Snapshots from the simulation should be included in your report.

- When writing the lab report, ensure that all sentences are grammatically correct & without mistakes in spelling. You can use a computer to make your report, the following powerful softwares may help you:

- SmartDraw or Microsoft Visio: to create and draw diagrams.

- Logisim: to enter and simulate logic circuits. (available at: <u>http://www.cburch.com/logisim/</u>). Similar tools are Logicly (available at <u>http://logic.ly/</u>). Circuit maker (available at <u>http://circuitmaker.com/</u>), Multisim (available at <u>http://www.ni.com/multisim/</u>), and Xilinx ISE (available at <u>http://www.xilinx.com</u>).

- Please ask the instructor if any point here is not clear to you.

This page is intentionally left blank

## Weekly Schedule

## (Based on the University Calendar)

| Week | Lab/Tutorial                                                                       |

|------|------------------------------------------------------------------------------------|

| 1    | No lab nor tutorial                                                                |

| 2    | Tutorial 1: Number systems – Conversions                                           |

| 3    | Tutorial 2: Number systems – Operations and Codes                                  |

| 4    | Experiment 1: Introduction to logic gates                                          |

| 5    | Tutorial 3: Implementation and simplification of Boolean functions using           |

|      | Boolean Algebra                                                                    |

| 6    | Experiment 2: Implementation and Simplification of Boolean functions               |

| 7    | Experiment 3: NAND and NOR implementation                                          |

| 8    | Tutorial 4: Implementation and simplification of Boolean functions using K-        |

|      | maps                                                                               |

| 9    | Reading Break                                                                      |

| 10   | Experiment 4: Combinational logic modules – Adders and subtractors                 |

| 11   | Experiment 5: Combinational logic modules – Decoders                               |

| 12   | Experiment 6: Combinational logic modules – Comparators and multiplexers           |

| 13   | <b>Experiment 7:</b> Exam on Combinational logic modules – Design of an arithmetic |

|      | circuit                                                                            |

| 14   | Tutorial 5: Sequential logic, flip flops, FSM analysis and design                  |

| 15   | Experiment 8: Latches, Flip flops and counters                                     |

| 16   | Final Lab Exam                                                                     |

## Week (2)

## **Tutorial 1: Number systems – Conversions**

Reminder: Please, remember to print and bring the tutorial with you

## Week (3)

## **Tutorial 2: Number systems – Operations and Codes**

Reminder: Please, remember to print and bring the tutorial with you

## Week (4)

## **Experiment 1: Introduction to Logic Gates**

## 1.1 Objectives:

- To get familiar with the usage of the lab software and equipments.

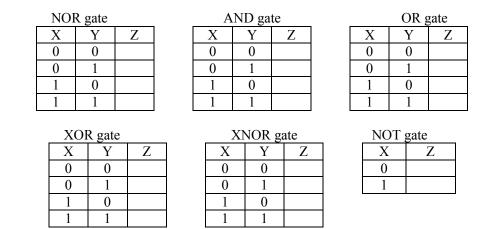

- To describe and verify the operation of AND, OR, NOT, NAND, NOR, XOR, and XNOR gates.

- To introduce a basic knowledge of Integrated Circuits (ICs) operation.

- To practice how to simulate a simple digital circuit using a software package and to build it using ICs and other digital components.

## 1.2 Background Information:

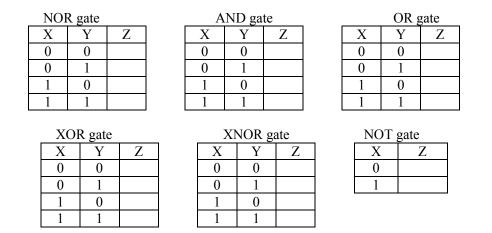

Logic gates are the simplest component of any logic circuit. In order to understand the computer logic, you should understand and master the logic operators (i.e., gates). A gate is a digital electronic circuit having only one output, but one or more inputs. The output that appears at the output of the gate depends on the input combinations.

There are many types of logic gates; such as AND, OR, and NOT, which are usually called the three basic gates. Other popular gates are NAND and NOR gates; which are simply combinations of an AND or an OR gate followed by a NOT gate. Other gates include the XOR "Exclusive-OR" and the XNOR "Exclusive NOR" gates. In this experiment, we will investigate the above mentioned basic logic gates and study their operations according to their truth table, as prescribed during lectures.

## **1.3 Equipment Required:**

- 1.3.1 Software simulation: The Logisim software package is installed on every PC in the lab.

- 1.3.2 Hardware implementation: The following equipment are needed to perform all the procedures:

- IC Training Kit

- Jumper wire kit

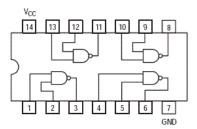

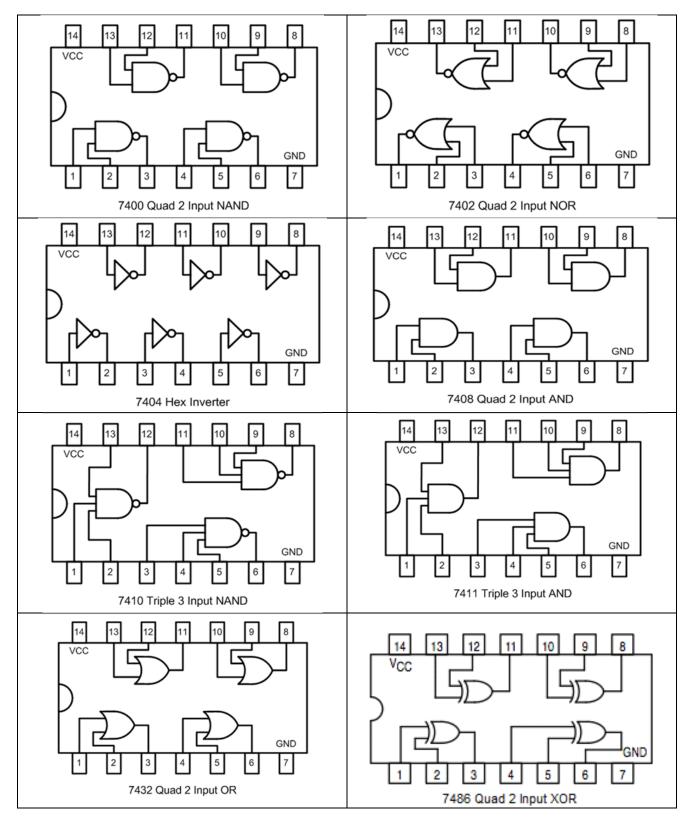

- 1x 7400 TTL QUAD NAND GATE

- 1x 7402 TTL QUAD NOR GATE

- 1x 7404 TTL HEX INVERTER GATE

- 1x 7408 TTL QUAD AND GATE

- 1x 7432 TTL QUAD OR GATE

- 1x 7486 TTL QUAD EXCLUSIVE OR GATE

- 1x 74266 TTL QUAD EXCLUSIVE NOR GATE

- 2x Toggle Switches

- 1x Carbon-film Resistor (470 $\Omega$ )

- 1x LED

### 1.4 Prelab:

It is recommended that you go through the Logisim beginners tutorial before coming to the lab. The tutorial is available at <u>http://www.cburch.com/logisim/docs/2.7/en/html/guide/tutorial/index.html</u>.

### 1.5 Software Simulation:

- 1.5.1 Login into one of the PCs in the lab using your user name and password.

- 1.5.2 Double click on the *logisim-win-2.7.1* icon on the desktop of the computer.

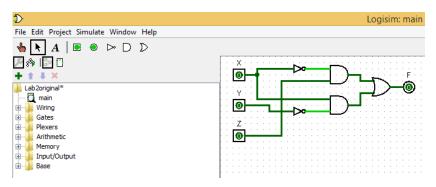

1.5.3 The Logisim main window will open, as shown below

|                                                                                                | Logisim: main of Untitled 🛛 🗕 🖻 💌 |

|------------------------------------------------------------------------------------------------|-----------------------------------|

| Edit Project Simulate Window Help                                                              |                                   |

|                                                                                                |                                   |

|                                                                                                |                                   |

| • A   ■ ● ▷ D D                                                                                |                                   |

| Untitled<br>main<br>Wining<br>Gates<br>Plexers<br>Arthreatic<br>Memory<br>Irput/Output<br>Base |                                   |

| Gates<br>Plexers<br>Arithmetic                                                                 |                                   |

| Memory<br>Input/Output                                                                         |                                   |

| ase base                                                                                       |                                   |

|                                                                                                |                                   |

|                                                                                                |                                   |

|                                                                                                |                                   |

|                                                                                                |                                   |

|                                                                                                |                                   |

|                                                                                                |                                   |

|                                                                                                |                                   |

|                                                                                                |                                   |

|                                                                                                |                                   |

|                                                                                                |                                   |

| %                                                                                              |                                   |

- 1.5.4 Logisim main window has five main parts:

- Explorer pane that includes the components, which you will use in building your design.

- Attribute table that allows you to adjust the attribute of the components, according to your design needs. If the attribute table is not apparent on your computer right now, it will show up in the following steps.

- Canvas, where you will draw your circuit

- Menu bar that allow you to handle you project and its associated files

- Toolbar that helps you to draw and simulate your circuit

| D Logisim: main of Untitle<br>File Menue Barulat |                | Help                        |                   |                       |

|--------------------------------------------------|----------------|-----------------------------|-------------------|-----------------------|

| Toolbar                                          | ⊳ D_           |                             |                   |                       |

| Exptorer                                         |                | Canvas                      | · · · · · · · ·   |                       |

| + Pane                                           | <b>_</b> : : : |                             |                   |                       |

| Untitled                                         |                | · · · · · · · · · · · · · · | · · · · · · · · · | · · · · · · · · · · · |

|                                                  | - <b>-</b>     |                             |                   |                       |

| + Plexers                                        |                |                             |                   |                       |

| Attribute                                        |                |                             | · · · · · · · ·   |                       |

| Circuit Nam <b>Table</b><br>Shared Label         |                |                             |                   |                       |

| Shared Label East                                |                | · · · · · · · · · · · · ·   | · · · · · · · ·   |                       |

| 100%                                             | <b>_</b>       |                             |                   |                       |

The picture is taken from

http://www.cburch.com/logisim/docs/2.7/en/html/guide/tutorial/tutor-orient.html.

1.5.5 From the File menu, click on *Save* or simply click Ctrl+S.

| $\mathcal{D}$ |              |          |        |      |

|---------------|--------------|----------|--------|------|

| File          | Edit Project | Simulate | Window | Help |

|               | New          | Ctrl+N   |        | D    |

|               | Open         | Ctrl+O   |        |      |

|               | Open Recent  |          | +      |      |

|               | Close        | Ctrl+SI  | hift+W |      |

|               | Save         | Ctrl+S   |        |      |

|               | Save As      | Ctrl+S   | hift+S |      |

|               | Export Image |          |        |      |

|               | Print        | Ctrl+P   |        |      |

|               | Preferences  |          |        |      |

|               | Exit         | Ctrl+Q   |        |      |

1.5.6 The <u>Save</u> window will show up. Browse to the folder, where you want to save you files, write lab1 on the *File name*, then click save.

| Ð            |                | Save                     |   |         | ×    |

|--------------|----------------|--------------------------|---|---------|------|

| Save in:     | 퉬 Labs         |                          | ~ | 🏂 📂 🛄 - |      |

| Recent Items | 🍌 lab1         |                          |   |         |      |

| Desktop      |                |                          |   |         |      |

| Documents    |                |                          |   |         |      |

| This PC      |                |                          |   |         |      |

|              | File name:     | lab 1                    |   | Ор      | en   |

| Network      | Files of type: | Logisim Project (*.circ) |   | ✓ Car   | ncel |

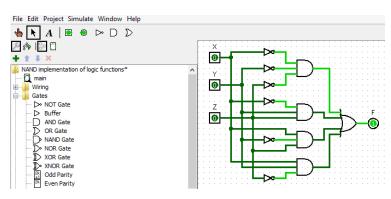

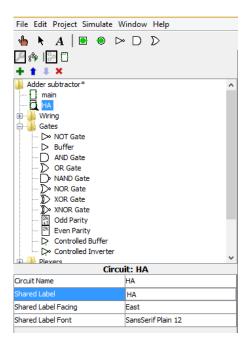

1.5.7 Now, you are ready to verify the operation of all basic logic gates. Let's start with the NAND gate.1.5.8 From the *explorer pane*, expand the *Gates* folder by clicking on the + sign beside it.

| $\mathcal{D}$                          |    |

|----------------------------------------|----|

| File Edit Project Simulate Window Help |    |

| A ■ A ■ ● D D                          |    |

| 2010                                   |    |

| + 1 ¥ ×                                |    |

| 퉬 lab1                                 | ~  |

| — 🖸 main                               |    |

| 😟 - 🚹 Wiring                           |    |

| 🚊 🌗 Gates                              |    |

| 🗁 NOT Gate                             |    |

| - D Buffer                             |    |

| D AND Gate                             | E. |

| D OR Gate                              |    |

| D NAND Gate                            |    |

| De NOR Gate                            |    |

| - D XOR Gate                           |    |

| 🔊 XNOR Gate                            |    |

| Odd Parity                             |    |

| 🕅 Even Parity                          |    |

| Controlled Buffer                      |    |

| Controlled Inverter                    |    |

| Plexers                                |    |

| 🞰 🕒 Arithmetic                         | ×  |

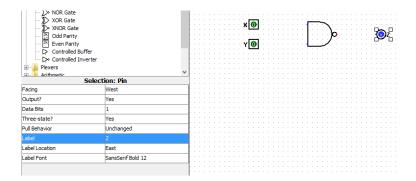

1.5.9 Select the NAND gate and place it onto the *canvas*. Notice that the attribute table of the NAND gate would show up.

| Data Bits     1       Gate Size     Medium       Number Of Inputs     S       Dutput Value     0/1       Jabel     J       Jabel Font     SansSerif Plain 12       Vegate 1 (Top)     No       Vegate 2     No       Vegate 3     No       Vegate 5 (Bottom)     No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | File Edit Project Simulate W          | √indow Help        |                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------|----------------------------------------|

| Idel1*         Imain         Wring         Gates         Imain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 👆 📐 A   🖻 🔹 ⊳                         | • D D              |                                        |

| Idel1*         Imain         Wring         Gates         Imain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                    |                                        |

| Ida1*       Ida1*         Id                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                       |                    |                                        |

| Wring         Gates         >> NOT Gate         >> AND Gate         >> NOR Gate         >> Contoled Buffer         >> Contoled Buffer         >> Pexers         >> Contoled Inverter         Pexers         >> Controled Inverter         >> Pexers         >> Controled Inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | · · · · · · · · · · · · · · · · · · · |                    |                                        |

| Gates         Gates         Buffer         AND Gate         OR Gate         NAND Gate         NoR Gate         Non Controled Duffer         Pepers         Pepers         Selection:         Namber of Inputs         S         Dutput Value         0/1         .abel         .abel Font         SansSenf Plain 12         Vegate 1 (Top)         No         Vegate 2       No         Vegate 3       No         Vegate 4       No         Vegate 5 (Bottom)       No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       | ~                  | • • • • • • • • • • • • • • • • • • •  |

| → NOT Gate         → Buffer         → AND Gate         → NAND Gate         → NOR Gate         → Controlled Differ         > Selection:         Number Of Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       |                    |                                        |

| → NOT Gate         → Buffer         → AND Gate         → NAND Gate         → NOR Gate         → Controlled Differ         > Selection:         Number Of Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Gates                                 |                    |                                        |

| Perfor       AND Gate         O CR Gate       NAND Gate         NAND Gate       NAND Gate         NAND Gate       NAND Gate         NOR Gate       NAND Gate         NOR Gate       NAND Gate         NOR Gate       NAND Gate         Nornoled Buffer       Image: Controled Buffer         Percent       Selection: NAND Gate         Percent       Selection: NAND Gate         Pactification       Selection: NAND Gate         Fading       East         Data Bits       1         Data Bits       1         Data Bits       1         Dutput Value       0/1         .abel Font       SansSerif Plain 12         Vegate 1       No         Vegate 2       No         Vegate 3       No         Vegate 4       No         Vegate 5 (Bottom)       No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |                    |                                        |

| AND Gate OR Gate NNR Gate NNR Gate NNR Gate NNR Gate NNR Gate NNR Gate OddParity Plevers Addmetic Rection: NAND Gate Controlled Inverter Plevers Addmetic Selection: NAND Gate Controlled Inverter Plevers Addmetic Plevers Addmetic Selection: NAND Gate Controlled Inverter Controlled Inver |                                       |                    |                                        |

| NND Gate         > NOR Gate         > XNOR Gate         > XNOR Gate         O dd Party         > Controlled Differ         > Controled Differ         > Contro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                    |                                        |

| NOR Gate         XOR Gate         XOR Gate         Odd Parity         Even Parity         Controlled Buffer         Peers         Controlled Inverter         Selection: NAND Gate         Peers         Selection: NAND Gate         Selection: NAND Gate         Paing         East         Data Bits         1         Sate Size         Medum         Number Of Inputs         S         Dutput Value         0/1         .abel         .abel Font         SansSenf Plan 12         Vegate 2         No         Vegate 3         No         Vegate 4         No         Vegate 5 (Bottom)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | - DR Gate                             |                    |                                        |

| > XOR Gate         > XNOR Gate         > Qod Parity         > Even Parity         > Controlled Buffer         >> Controlled B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |                    |                                        |

| Image: State of the state                                 |                                       |                    |                                        |

| Image: Selection: NAND Gate         Facing       East         Selection: NAND Gate         Facing       East         Data Bits       1         Data Sits       1         Data Sits       1         Data Bits       1         Label                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       |                    |                                        |

| Controlled Inffer         U         U           Plexers         V           Selection: NAND Gate         Selection: NAND Gate           Page 2         Medum           Sate Size         Medum           Number Of Inputs         5           Dutput Value         0/1           .abel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       |                    | ······································ |

| Controlled Inffer         U         U           Plexers         V           Selection: NAND Gate         Selection: NAND Gate           Page 2         Medum           Sate Size         Medum           Number Of Inputs         5           Dutput Value         0/1           .abel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2k<br>+1 Odd Parity                   |                    | P                                      |

| Decontrolled Inverter         Selection:         NAID Gate           ading         East           ading         East           Data Bits         1           Sate Size         Medium           Number Of Inputs         5           Dutput Value         0/1           .abel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |                    | ↓                                      |

| Pervers         V           Selection: NAND Gate           adng         East           Data Bits         1           Sate Size         Medum           Number Of Inputs         S           Output Value         0/1           Jubel All         SansSerif Plain 12           Vegate 1 (Top)         No           Vegate 3         No           Vegate 5 (Bottom)         No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                       |                    |                                        |

| Selection:         NAND Gate           Fading         East           Tata Bits         1           Gate Size         Medum           Number Of Inputs         5           Dutput Value         0/1           .abel Font         SansSerif Plain 12           Vegate 1 (Top)         No           Vegate 2         No           Vegate 3         No           Vegate 5 (Bottom)         No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |                    |                                        |

| Selection:         NAND Gate           Facing         East           Facing         East           Jata Bits         1           Sate Size         Medium           Number Of Inputs         5           Output Value         0/1           Jabel         5           Jabel Font         SansSenf Plain 12           Vegate 2         No           Vegate 3         No           Vegate 5 (Bottom)         No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |                    |                                        |

| Facing         East           Data Bits         1           Sate Size         Medum           Wumber Of Inputs         S           Dutput Value         O/1           .abel         o/1           .abel Font         SansSenif Plain 12           Vegate 1 (Top)         No           Negate 2         No           Negate 3         No           Vegate 5 (Bottom)         No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Selection:                            | NAND Gate          |                                        |

| Gate Size         Medum           Number Of Inputs         S           Output Value         O/1           Jabel         Image: Stream of the stre                                                                                                                                          |                                       |                    | 7                                      |

| Number Of Inputs         5           Dutput Value         0/1           abel            .abel Font         SansSenf Plan 12           Vegate 1 (Top)         No           Vegate 2         No           Vegate 3         No           Vegate 4         No           Vegate 5 (Bottom)         No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Data Bits                             | 1                  | -                                      |

| Dutput Value         0/1           .abel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Gate Size                             | Medium             | ■                                      |

| Dutput Value         0/1           .abel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Number Of Inputs                      | 5                  |                                        |

| Label SansSenif Plain 12<br>Vegate 1 (Top) No<br>Vegate 2 No<br>Vegate 3 No<br>Vegate 4 No<br>Vegate 5 (Bottom) No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       | 0/1                | =                                      |

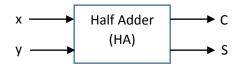

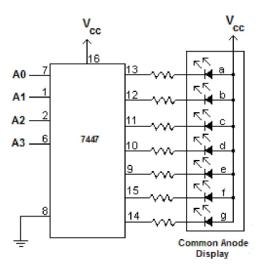

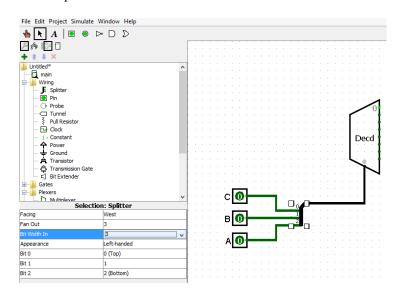

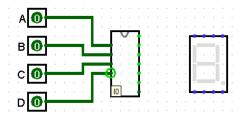

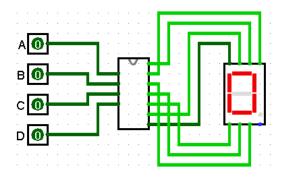

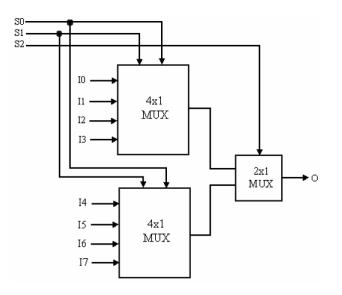

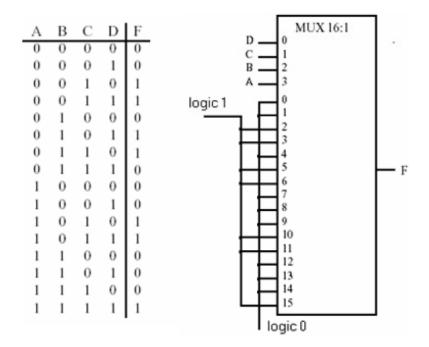

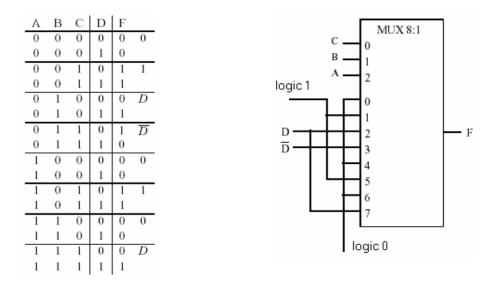

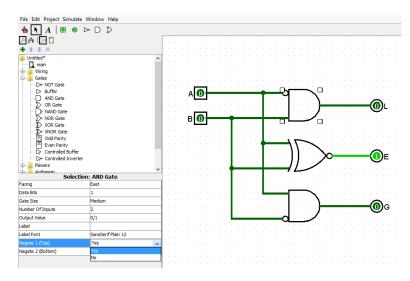

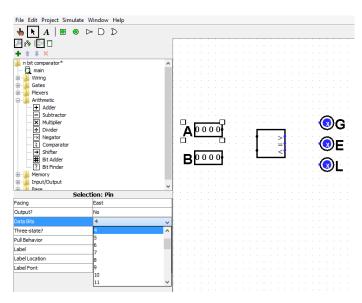

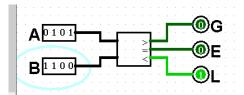

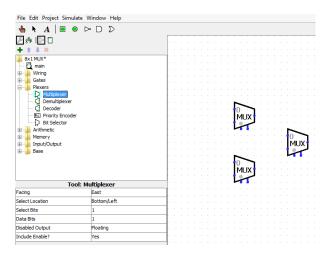

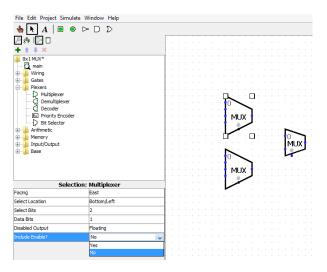

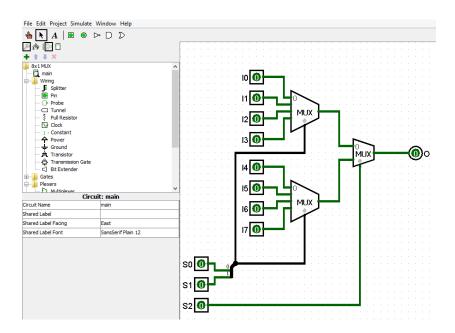

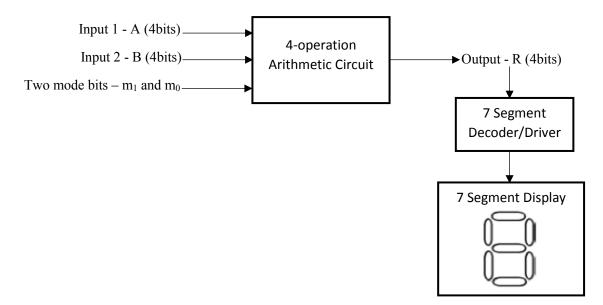

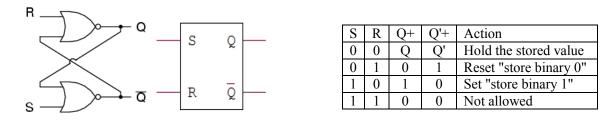

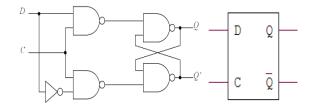

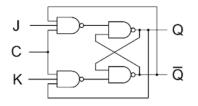

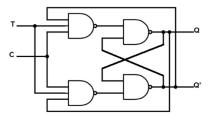

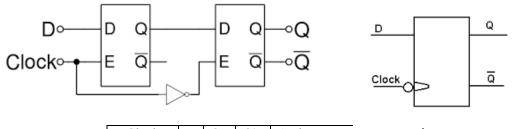

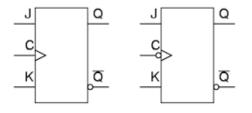

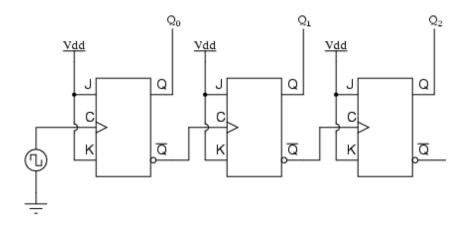

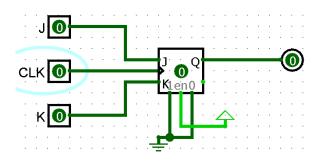

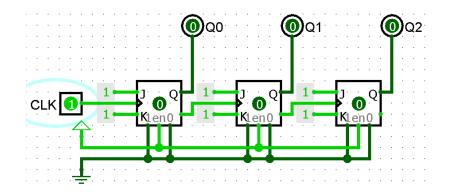

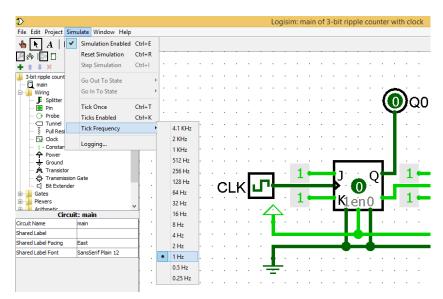

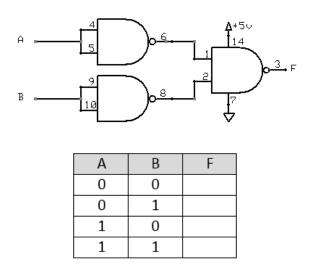

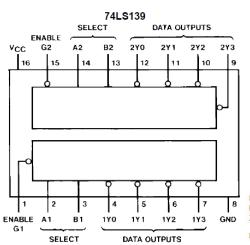

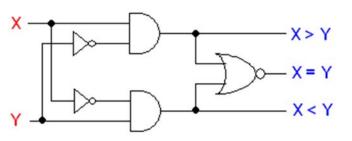

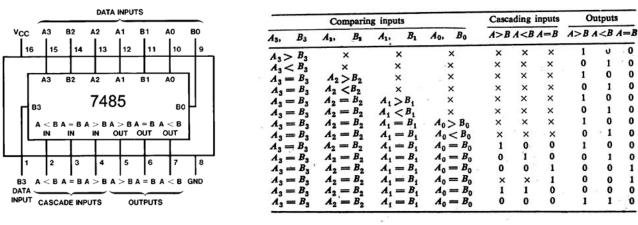

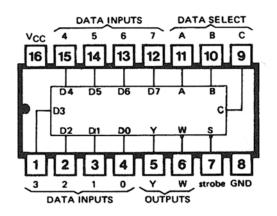

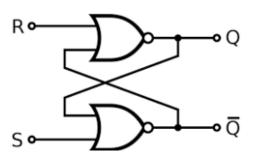

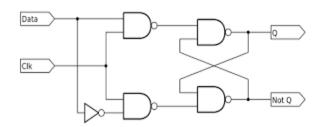

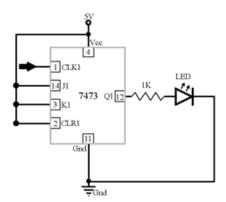

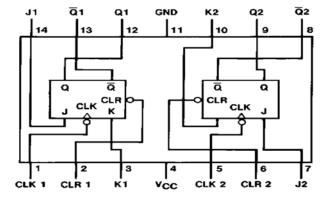

| abel Font     SansSenf Plan 12       Negate 1 (Top)     No       Vegate 2     No       Vegate 3     No       Vegate 4     No       Vegate 5 (Bottom)     No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       |                    | -                                      |