# New Hardware Algorithms and Designs for Montgomery Modular Inverse Computation in Galois Fields GF(p) and GF(2<sup>n</sup>)

by

Adnan Abdul-Aziz Gutub

# PhD Thesis

Electrical and Computer Engineering Oregon State University Corvallis, Oregon, USA

June 11, 2002

#### AN ABSTRACT OF THE THESIS OF

Adnan Abdul-Aziz Gutub for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer Engineering</u> presented on <u>June 11, 2002</u>.

Title: New Hardware Algorithms and Designs for Montgomery Modular Inverse Computation in Galois Fields GF(p) and GF(2<sup>n</sup>).

| Abstract approved: |                          |

|--------------------|--------------------------|

|                    | Alexandre Ferreira Tenca |

The computation of the inverse of a number in finite fields, namely Galois Fields GF(p) or GF(2<sup>n</sup>), is one of the most complex arithmetic operations in cryptographic applications. In this work, we investigate the GF(p) inversion and present several phases in the design of efficient hardware implementations to compute the Montgomery modular inverse. We suggest a new correction phase for a previously proposed almost Montgomery inverse algorithm to calculate the inversion in hardware. It is also presented how to obtain a fast hardware algorithm to compute the inverse by multi-bit shifting method. The proposed designs have the hardware scalability feature, which means that the design can fit on constrained areas and still handle operands of any size. In order to have long-precision calculations, the module works on small precision words. The word-size, on which the module operates, can be selected based on the area and performance requirements. The upper limit on the operand precision is dictated only by the available memory to store the operands and internal results. The scalable module is in principle capable of performing infinite-precision Montgomery inverse computation of an integer, modulo a prime number.

We also propose a scalable and unified architecture for a Montgomery inverse hardware that operates in both GF(p) and  $GF(2^n)$  fields. We adjust and modify a  $GF(2^n)$  Montgomery inverse algorithm to benefit from multi-bit shifting hardware features making it very similar to the proposed best design of GF(p) inversion hardware.

We compare all scalable designs with fully parallel ones based on the same basic inversion algorithm. All scalable designs consumed less area and in general showed better performance than the fully parallel ones, which makes the scalable design a very efficient solution for computing the long precision Montgomery inverse.

©Copyright by Adnan Abdul-Aziz Gutub

June 11, 2002

All Rights Reserved

# New Hardware Algorithms and Designs for Montgomery Modular Inverse Computation in Galois Fields GF(p) and $GF(2^n)$

by

Adnan Abdul-Aziz Gutub

A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented June 11, 2002 Commencement June 2003

| <u>Doctor of Philosophy</u> thesis of <u>Adnan Abdul-Aziz Gutub</u> presented on <u>June 11, 2002</u>                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APPROVED:                                                                                                                                                                            |

|                                                                                                                                                                                      |

| Major Professor, representing Electrical and Computer Engineering                                                                                                                    |

|                                                                                                                                                                                      |

| Chair of the Department of Electrical and Computer Engineering                                                                                                                       |

|                                                                                                                                                                                      |

| Dean of the Graduate School                                                                                                                                                          |

|                                                                                                                                                                                      |

| I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon |

| request.                                                                                                                                                                             |

|                                                                                                                                                                                      |

| Adnan Abdul-Aziz Gutub, Author                                                                                                                                                       |

#### **ACKNOWLEDGMENTS**

I am grateful to my advisor Alexandre Ferreira Tenca for his reviews, help, guidance and encouragement in conducting this research and producing the papers that formed a basis for this thesis. I also thank Çetin Kaya Koç for his assistance in proposing my research topic, and his valuable directions toward this accomplishment. I also thank the other members of my graduate committee for their valuable input.

A number of people have given me invaluable technical help, recommendations and comments at various stages in the writing of these papers. In this regard I am thankful to the Information Security Laboratory researchers of Oregon State University. In particular, I acknowledge Roger Traylor, Erkay Savas, Tugrul Yanik, Budiyoso Kurniawan, Serdar Erdem, Don Heer, and Colin Van Dyke, for providing valuable support and feedback during different research phases.

I acknowledge financial support for my PhD education from KFUPM-Saudi Arabia and NSF under the CAREER grant CCR-0093434-"Computer Arithmetic Algorithms and Scalable Hardware Designs for Cryptographic Applications".

Finally, I owe a debt of gratitude to the rosy part in my life my great parents (Amnah Sait and Abdul-Aziz Kutub), my wonderful wife (Manal Fattani), and my lovely children (Muna, Alaa, and Omar), without them being patient, this achievement could not have been achieved.

Adnan Abdul-Aziz Gutub Corvallis, Oregon, USA June 11, 2002

# TABLE OF CONTENTS

|        |     |                                                                                   | <u>Page</u> |

|--------|-----|-----------------------------------------------------------------------------------|-------------|

| 1      | IN  | NTRODUCTION                                                                       | 1           |

|        | 1.1 | Motivation                                                                        | 5           |

|        | 1.2 | Previous Work                                                                     | 6           |

|        | 1.3 | Thesis Outline                                                                    | 7           |

| 2      | E   | LLIPTIC CURVE CRYPTOGRAPHY                                                        | 9           |

|        | 2.1 | Introduction                                                                      | 9           |

|        | 2.2 | Elliptic Curve Theory                                                             | 9           |

|        | 2.3 | Elliptic Curve Cryptography Applications                                          | 17          |

| 3<br>N |     | CALABLE HARDWARE ARCHITECTURE FOR GF(p) ALMOST GOMERY MODULAR INVERSE COMPUTATION | 20          |

|        | 3.1 | Introduction                                                                      | 20          |

|        | 3.2 | Montgomery Inverse Algorithms                                                     | 21          |

|        | 3.3 | The Fixed Precision Design                                                        | 24          |

|        | 3.4 | The Scalable Design                                                               | 27          |

|        | 3.5 | Modeling and Analysis                                                             | 32          |

|        | 3.6 | Summary                                                                           | 40          |

| 4<br>П |     | EDUCING THE CLOCK PERIOD OF THE ALMOST MONTGOMERY SE HARDWARE DESIGNS             | 41          |

|        | 4.1 | Introduction                                                                      | 41          |

|        | 4.2 | Shortening the Critical Path                                                      | 41          |

|        | 4.3 | Area & Delay Comparison                                                           | 42          |

# TABLE OF CONTENTS (Continued)

|         |       | ]                                                                                       | Page |

|---------|-------|-----------------------------------------------------------------------------------------|------|

| 5<br>IN |       | SCALABLE HARDWARE ARCHITECTURE FOR MONTGOMERY RSION IN GF(p)                            | 45   |

|         | 5.1   | Introduction                                                                            | 45   |

|         | 5.2   | Montgomery Inverse Algorithm and Proposed Modifications                                 | 45   |

|         | 5.3   | Multi-Bit Shifting.                                                                     | 48   |

|         | 5.4   | The Scalable Design                                                                     | 54   |

|         | 5.5   | Modeling and Analysis                                                                   | 58   |

| 6<br>IN |       | CALABLE AND UNIFIED HARDWARE TO COMPUTE MONTGOMERY RSE IN GF(p) AND GF(2 <sup>n</sup> ) | 65   |

|         | 6.1   | Introduction                                                                            | 65   |

|         | 6.2   | Montgomery Inverse Hardware Procedures For $GF(p)$ and $GF(2^n)$                        | 66   |

|         | 6.3   | Unified and Scalable Inverter Architecture.                                             | 71   |

|         | 6.4   | Modeling and Analysis                                                                   | 75   |

|         | 6.5   | Summary                                                                                 | 79   |

| 7       | C     | ONCLUSIONS AND FUTURE WORK                                                              | 81   |

|         | 7.1   | Conclusions                                                                             | 81   |

|         | 7.2   | Future Work                                                                             | 82   |

| В       | IBLI( | OGRAPHY                                                                                 | 84   |

| A       | PPEN  | NDICES                                                                                  | 84   |

| A       | Т     | HE EXTENDED EUCLIDEAN ALGORITHM                                                         | 89   |

| R       | G     | E(2 <sup>n</sup> ) NUMERICAL EXAMPLE VERIFICATION                                       | 93   |

# LIST OF FIGURES

| <u>Figu</u> | <u>re</u>                                                                      | <u>Page</u> |

|-------------|--------------------------------------------------------------------------------|-------------|

| 1.1         | Secret key cryptosystem                                                        | 2           |

| 1.2         | Public key cryptosystem                                                        | 3           |

| 3.1         | Types of input/output numbers for Kaliski algorithm                            | 21          |

| 3.2         | The complete Montgomery modular inverse hardware                               | 23          |

| 3.3         | The block diagram of implementing the FHW-Alg                                  | 26          |

| 3.4         | The fixed precision hardware data path                                         | 26          |

| 3.5         | The scalable hardware overall block diagram                                    | 29          |

| 3.6         | The scalable add/subtract unit                                                 | 30          |

| 3.7         | The scalable hardware shifter.                                                 | 31          |

| 3.8         | The data router configurations                                                 | 31          |

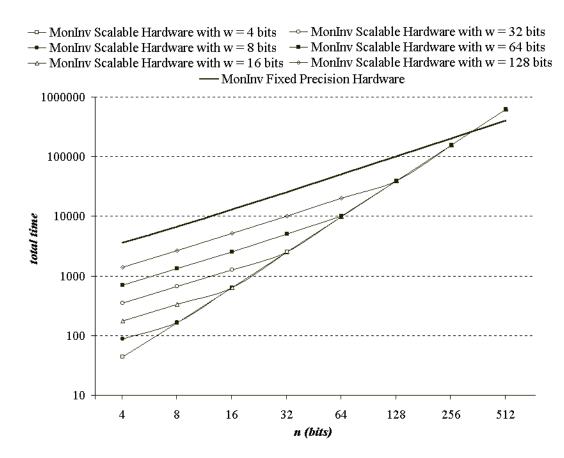

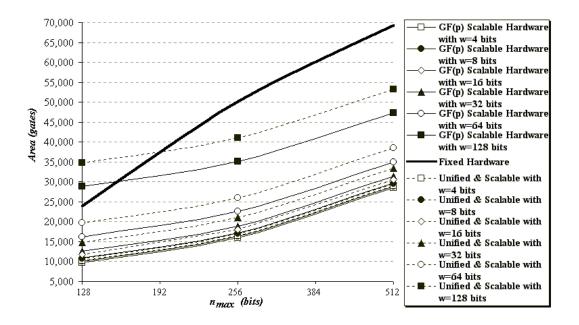

| 3.9         | The area comparison                                                            | 34          |

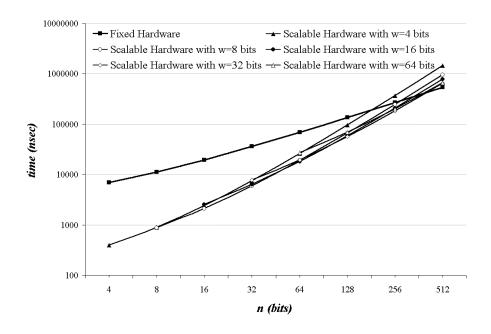

| 3.10        | Delay comparison of designs with $n_{max} = 256$ bits                          | 37          |

| 3.11        | 1 Delay comparison of designs with $n_{max} = 512$ bits                        | 38          |

| 3.12        | 2 Technology independent speed comparison for designs with $n_{max}$ =512 bits | 39          |

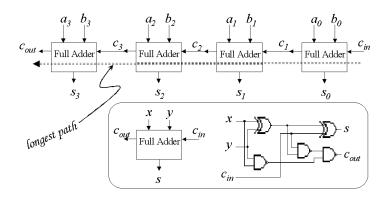

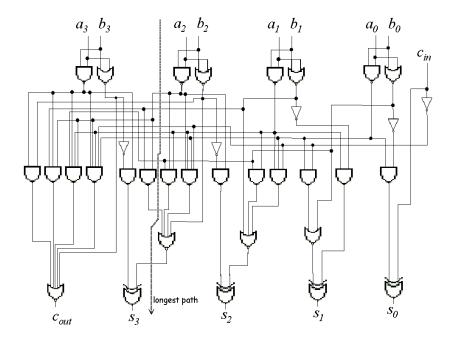

| 4.1         | The carry-ripple adder                                                         | 42          |

| 4.2         | A four bit carry-look-ahead adder                                              | 42          |

| 5.1         | Different ways to compute the Montgomery inversion                             | 48          |

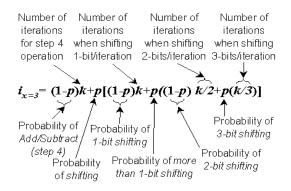

| 5.2         | Description of $i$ for the case of $x = 3$                                     | 51          |

| 5.3         | Montgomery inverse scalable hardware block diagram                             | 55          |

| 5.4         | Add/subtract unit                                                              | 57          |

| 5.5         | Multi-bit shifter (max distance = 3)                                           | 57          |

| 5.6         | Data router configurations.                                                    | 58          |

# LIST OF FIGURES (Continued)

| Figu | <u>Pa</u>                                                                        | <u>ge</u> |

|------|----------------------------------------------------------------------------------|-----------|

| 5.7  | Area comparison                                                                  | 60        |

| 5.8  | Delay comparison of designs with $n_{max} = 512$ bits                            | 63        |

| 5.9  | Technology independent speed comparison for all designs with $n_{max}$ =512 bits | 64        |

| 6.1  | Montgomery inverse hardware algorithm for GF(p)                                  | 67        |

| 6.2  | GF(2 <sup>n</sup> ) Montgomery inverse algorithm in its binary representation    | 69        |

| 6.3  | GF(2 <sup>n</sup> ) MonInv computation numerical example                         | 70        |

| 6.4  | Montgomery inverse hardware algorithm for GF(2 <sup>n</sup> )                    | 71        |

| 6.5  | Scalable and unified inverter hardware                                           | 73        |

| 6.6  | Add/Subtract unit of the scalable and unified hardware                           | 74        |

| 6.7  | Data router configurations.                                                      | 75        |

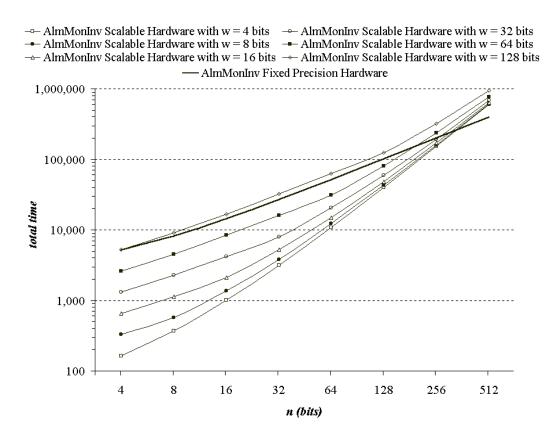

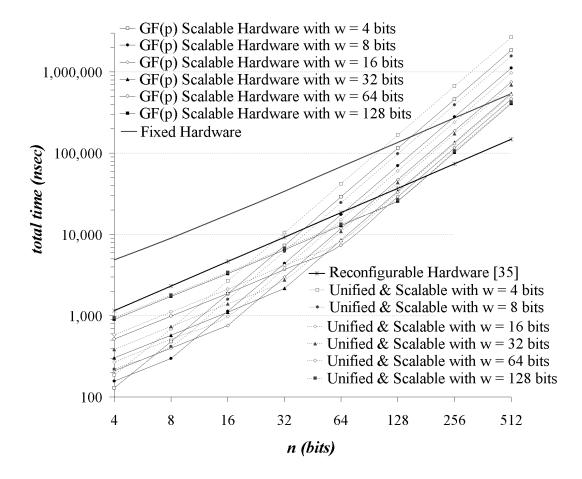

| 6.8  | Area comparison                                                                  | 76        |

| 6.9  | Delay comparison of designs with $n_{max} = 512$ bits                            | 78        |

# LIST OF TABLES

| Tabl | <u>e</u>                                                                                             | <u>Page</u> |

|------|------------------------------------------------------------------------------------------------------|-------------|

| 1.1  | Area and time complexity of different inversion hardware designs                                     | 6           |

| 2.1  | Comparing GF(p) and GF(2 <sup>n</sup> ) number of lengthy point operations in affine coordinates     | 14          |

| 2.2  | Comparing GF(p) and GF(2 <sup>n</sup> ) number of lengthy point operations in projective coordinates | 15          |

| 2.3  | Comparing the affine and projective coordinates                                                      | 17          |

| 3.1  | Area of the standard logic gates                                                                     | 33          |

| 3.2  | Area of the modules building the memory unit of the scalable design                                  | 33          |

| 3.3  | Clock cycle period for all designs (nsec)                                                            | 36          |

| 3.4  | Adders $\delta$ delay estimation depending on the number of bits                                     | 38          |

| 4.1  | Area and delay optimizations of the AlmMonInv scalable design                                        | 43          |

| 4.2  | Area and delay optimizations of the AlmMonInv fixed precision design                                 | 44          |

| 5.1  | Delay of different ways to compute the Montgomery inverse                                            | 48          |

| 5.2  | Average number of iterations (i)                                                                     | 50          |

| 5.3  | Speed and hardware changes due to multi-bit shifting the CorPh algorithm                             | 53          |

| 5.4  | Clock cycle period for scalable designs (nsec)                                                       | 60          |

| 5.5  | Clock cycle period for fixed designs (nsec)                                                          | 60          |

# NEW HARDWARE ALGORITHMS AND DESIGNS FOR MONTGOMERY MODULAR INVERSE COMPUTATION IN GALOIS FIELDS GF(p) AND GF(2<sup>n</sup>)

#### I INTRODUCTION

Information security nowadays is a very important subject [32,40,41]. Governments, commercial businesses, and individuals are all demanding secure information in electronic documents, which is becoming preferred over traditional documents (paper and microfilm, for example). Documents in electronic form require less storage space, its transfer is almost instantaneous, and it is accessible via simplified databases. The ability to make use of information more efficiently has resulted in a rapid increase in the value of information. Businesses in a number of commercial arenas recognize information as their most valuable asset [34].

However, information in electronic form faces potentially more damaging security threats. Unlike information printed on paper, information in electronic form can virtually be stolen from a remote location. It is much easier to alter and intercept electronic communication than its paper-based predecessors.

Information security is described as the set of measures taken to prevent unauthorized use of electronic data, whether this unauthorized use takes the form of disclosure, alteration, substitution, or destruction of the data. The requirements to securely maintain electronic information are classified as the following three services:

- *Confidentiality* hiding data from unauthorized parties.

- *Integrity* assurance that data is genuine.

- Availability the system still functions efficiently after security provisions are in place.

Several measures have been considered to provide these services but no single measure can ensure complete security [32]. Of the various proposed measures, the use of cryptographic systems offers the highest level of security, together with maximum flexibility [40,41]. A cryptographic system transforms electronic data into a modified form. The owner of the information in modified form is now assured of its security features. Depending on the security services required, the assurance may be that the data cannot be

altered without detection, or it may be that the data is unintelligible to all but authorized parties.

In the past, cryptographic systems have provided only confidentiality. Preparing a message for a secure, private transference involves the process of *encryption*. *Encryption* transforms data from user readable form, called *plaintext*, to an illegible translation, called *ciphertext*. The conversion of plaintext to ciphertext is controlled by an electronic key *E*. The key is simply a binary number, which determines the effect of the encryption function. The reverse process of retrieving the plaintext back from the ciphertext is called *decryption*, and is controlled by a related key *D*.

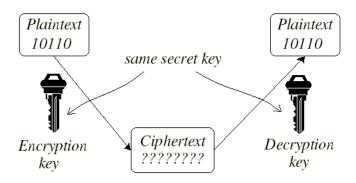

Depending on the encryption/decryption key, cryptographic systems can be classified into two main categories: secret key cryptosystems and public key cryptosystems. The secret key cryptosystems use one key (E=D) for both encryption and decryption, as illustrated in Figure 1.1. Since the keys are the same, two users wishing to communicate in confidence must agree and maintain a common secret key. Each entity must trust the other to keep the key as a secret.

Figure 1.1 Secret key cryptosystem

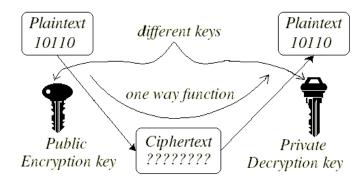

Public key cryptosystems, however, use two different keys, one for encryption (E) and the other for decryption (D), where  $D\neq E$ . Public key cryptosystems were introduced in 1976 by Whitfield Diffie and Martin Hellman [5]. In a public-key cryptosystem, the abilities to perform encryption and decryption are separated. The encryption needs a public

key (E) different but mathematically related to the decryption private key (D). Knowledge of the public key allows encryption of plaintext but does not allow decryption of the ciphertext. If somebody selects and publishes his public key, then everyone can use that public key to encrypt messages for that person. The private key is kept secret so that only the intended individual can decrypt the ciphertext. Figure 1.2 shows a public key cryptosystem methodology. One of the most promising public key cryptographic methods to be used is named the elliptic curve cryptography (ECC), which provides the best performance security of any public key cryptosystem known today [32,40,41]. ECC is based on the Discrete Logarithm problem over the points on an elliptic curve. In order to use ECC, an elliptic curve must be defined over a specific finite field. A finite field is a set of elements that have a finite order (number of elements). The order of a *Galois Field* (GF) is normally a prime number or a power of a prime number. The most popular finite fields used in ECC are *Galois Fields*, GF(p) and  $GF(2^n)$  [9-12,28,29].

Figure 1.2 Public key cryptosystem

ECC is heavily based on modular multiplication, which involves division by the modulus in its computations. Division, however, is a very expensive operation [13,14]. This characteristic of modular operations made researchers seek out methods to reduce the division impact and make modulo multiplication less time consuming. In 1985, P. Montgomery proposed an algorithm to perform modular multiplication without trial division [15]. The algorithm replaces the complex division with simple divisions by two,

which is effortlessly achieved in the binary representation of numbers (shifting the binary number one bit to the right). The penalty in using Montgomery's technique is paid with some extra computations to represent the multiplication operands into Montgomery domain and transform them back to integer domain [1,6,11,15]. The reader is referred to [15] for detailed information about Montgomery's method. A brief description of the Montgomery concept is provided in Chapter 3.

The ECC computation consists of different modular arithmetic operations where inversion is an essential one, with the slowest speed [1,2,9-12,20-25]. Since the use of Montgomery's method requires that the numbers are in Montgomery's domain, it is clear that having procedures dedicated to compute the modular inverse in the Montgomery domain [1,2] would be extremely beneficial. These dedicated modular inverse methods are named the Montgomery modular inverse algorithms.

Montgomery inverse (MonInv) computation can be performed in software or hardware for either GF(p) or GF(2<sup>n</sup>). In this thesis, one of our goals is to design an efficient scalable MonInv hardware to operate in both finite fields GF(p) and GF(2<sup>n</sup>). Scalability is the feature that allows the hardware to fit into restricted areas and operate with high clock frequency, which together are rarely possible for the fully parallel designs.

We start by considering the inverse computation in GF(p). It is well known that algorithms dedicated for GF(p) computation may be adjusted for GF(2<sup>n</sup>). However, it is very difficult to modify a GF(2<sup>n</sup>) algorithm for GF(p) [11,35]. The standard modular inverse over GF(p) can be defined by the following example. Assume a is an integer in the range [1,p-1]. Integer x is called the modular inverse, or modulo inverse, of integer a if-and-only-if:  $ax \equiv 1 \pmod{p}$ ; where  $x \in [1,p$ -1]. It is normally represented as  $x = a^{-1} \mod p$  [1]. The MonInv algorithm suitable for our research is portrayed in [1]. The algorithm requires two main operations: an *almost Montgomery inverse* (AlmMonInv) and a correction phase (Montgomery product) operation. Our study modifies this algorithm for hardware and introduces a new faster correction phase. A similar GF(2<sup>n</sup>) MonInv algorithm is also proposed, where both GF(p) and GF(2<sup>n</sup>) MonInv algorithms are designed as a unified MonInv hardware for GF(p) and GF(2<sup>n</sup>).

The motivation to focus our research on the design of inversion in hardware is explained in Section 1.1. Section 1.2 presents a brief review of the previous attempts to perform inversion in hardware. Section 1.3 details the thesis outline.

#### 1.1 Motivation

Modular inverse arithmetic is a fundamental arithmetic operation in public-key cryptography. It is used in the Diffie-Hellman key exchange method [5], and to calculate private decryption key for RSA [4]. Modular inversion is considered an essential operation in the elliptic curve cryptography (ECC) [1,2,9-12,20-25]. This research is targeted mainly toward the ECC utilization because of its promise to replace several older cryptographic systems [9-12,20]. ECC arithmetic consists mainly in modular computations of addition, subtraction, multiplication, and inversion.

Inversion is well known to be the slowest operation among all other arithmetic operations in ECC [1,2,11,16-18]. Many researchers propose minimizing the use of modular inversion by adopting elliptic curves defined for projective coordinates, which substitute the inverse by several multiplication operations [9-12]. Projective coordinates are one of two coordinate systems used for the ECC arithmetic point operations; the other one is known as affine [11] coordinate system (detailed in Chapter 2). Inversion, in the projective coordinate systems, is required only once, to convert the projective coordinate points to affine coordinates at the end of the ECC point computation. However, if this one use of inversion takes too long, it will affect the performance of the whole ECC system.

To have a fast modular inverse calculation is one of the main reasons to do inversion in hardware instead of software [16-18]. If it is possible to compute the inverse faster than nine multiplication operations, then it is more efficient to use the affine coordinate system instead of going to the projective coordinate systems, as discussed in Chapter 2. Even if the speed to compute the inverse is not that good to justify the use of affine coordinates, the computation with hardware is still faster than software [6,16-18,20-25], which will provide better performance for the overall cryptographic system based on projective coordinates.

The other main reason to implement the modular inverse operation in hardware is security [32]. For cryptographic applications, it is more secure to have all the computations handled in hardware, inside an IC-chip for example, instead of mixing some computations performed in software with others processed in hardware. Software implementations are supported by operating systems, which can be interrupted and trespassed by intruders and this way compromise the application security. Such a security threat is not so easily attained in hardware implementations [32].

#### 1.2 Previous Work

Modular inversion is often performed based on modifying, or directly using, the extended Euclidean algorithm [11]. Several inversion hardware attempts are described in the literature [16-18,20-25,35]. Most of the research [17,18,20-25] proposed hardware models specifically designed for inversion in GF(2<sup>n</sup>). Among them, the large architectures in [23,24] suffer from the problem of signal broadcasting. The signal broadcasting problem should be avoided when implementing high-speed VLSI circuits [17,39].

In contrast, the designs in [17,18,21,22,25] are based on the concept of parallel systolic array structures. A systolic array [39] consists of a set of interconnected logic cells, each capable of performing the same simple operation. They work together and synchronously to perform a task. Within a systolic array or tree, information and data flow between the cells in a pipelined regular mode. Although systolic arrays are well suited for VLSI implementations due to its modular identical cells and simple and regular communications and control structures, it normally consumes a huge amount of hardware area in order to gain computation speed [17]. The area and time complexities of the designs in [17,18,21,22,25] are listed in Table 1.1.

| Hardware Design                    | Area Complexity | Time Complexity |

|------------------------------------|-----------------|-----------------|

| Guo & Wang [17]                    | $O(n^2)$        | O(1)            |

| Choudhury & Barua [18]             | O(n)            | $O(n^2)$        |

| Guo & Wang [21]                    | $O(n^2)$        | O(1)            |

| Fenn, Benaissa & Tayler [22]       | $O(n^2)$        | O(n)            |

| Kovac, Ranganathan & Varanasi [25] | $O(n. n^2)$     | O(1)            |

Table 1.1 Area and time complexity of different inversion hardware designs

Hasan in [20] proposed a hardware design for the GF(2<sup>n</sup>) inversion algorithm in a non-systolic structure consuming smaller hardware area and still operating with reasonable speed. The large operands are divided into words. The hardware performs the computation on a word-by-word serial manner, instead of computing all the words in parallel. GF(2<sup>n</sup>) arithmetic requires simpler modular operations than GF(p) [11] because the carry

propagation delays in addition or subtractions are completely eliminated. Since we focus first on GF(p) and then extend it to  $GF(2^n)$ , the designs proposed for  $GF(2^n)$  in [17,18,21-25] were not beneficial to this work. As said before, extending a design done for  $GF(2^n)$  to GF(p) is not practical [11].

Naofumi Takagi in [16], proposed an inverse algorithm for hardware with a redundant binary representation. Redundant representation is used to reduce the carry propagation delay problem in additions. However, the redundant binary representation requires more area, because redundant digits require more bits to be coded and stored. Furthermore, redundant representation needs data transformation, which results in considerable extra cost.

Goodman and Chandrakasan in [35] presented a general cryptographic processor that computes modular algorithms coded in microcode, which can be modified with minimal effort. The processor can perform inversion in both GF(p) and GF(2<sup>n</sup>) finite fields. Its datapath is reconfigurable and parameterized for numbers ranging in size from 8 to 1024 bits, controlled by a shut-down unit. This unit is responsible for disabling unused portions of the data path in order to minimize any unnecessary power consumption. The processor hardware is designed carefully to be energy efficient and faster than software-based implementations. The main disadvantage of this processor is its huge area, with a core containing 880,000 devices.

#### 1.3 Thesis Outline

In the following chapter (Chapter 2), more detail is given to the ECC theory, which is the main scope of our research. The ECC arithmetic operations over the two finite fields GF(p) and  $GF(2^n)$  are compared. Then, some ECC based cryptographic applications are presented to give a practical flavor to the ECC theory.

A suitable GF(p) Montgomery inverse algorithm for hardware implementation was proposed in [1]. It requires two types of different routines, almost Montgomery inverse and Montgomery product. We present the design of the almost Montgomery inverse routine in Chapter 3. Two implementations are described there. The first one is a fixed precision (fully parallel) hardware, which has some inherent problems such as large (impractical)

area and very low clock frequency. To solve this problem, it is proposed to use a scalable hardware design that performs the same function operating with higher clock frequency. The scalable hardware is also a module that can handle operands of any size. Based on the hardware area and performance requirements, the word-size, on which the module operates, is selected. The upper limit on the operand precision is dictated only by the available memory to store the operands and internal results. The scalable module is in principle capable of performing infinite-precision Montgomery inverse computation of an integer, modulo a prime number. This scalable hardware is compared with the fixed precision design showing very attractive results.

The longest path of the hardware designs passes through adders and subtractors. Chapter 4 contains the analysis of the impact of faster adders and subtractors in the hardware. Experimental performance results for the designs (fixed precision and scalable) using carry-look-ahead adders instead of carry-ripple adders are presented.

In Chapter 5, we propose a complete GF(p) Montgomery inversion (MonInv) procedure (almost Montgomery inverse plus correction phase). We modify the original procedure presented in [1] by replacing the Montgomery product used in its correction phase by a new straightforward correction phase. The advantage of the new correction phase is that it is implemented with roughly the same scalable hardware of the almost Montgomery inverse algorithm described in Chapter 3. The concept of multiple-bit shifting is also introduced in the proposed MonInv design.

Chapter 6 proposes a scalable and unified architecture for a Montgomery inverse hardware that operates in both GF(p) and  $GF(2^n)$  fields. We present a  $GF(2^n)$  Montgomery inverse algorithm that accommodates multi-bit shifting making it very similar to the GF(p) algorithm of Chapter 5.

The conclusion chapter (Chapter 7) summarizes the results of this thesis work and provides some future work in this area.

#### 2 ELLIPTIC CURVE CRYPTOGRAPHY

### 2.1 Introduction

In 1985 Niel Koblitz and Victor Miller proposed the Elliptic Curve Cryptosystem (ECC) [9-11,28-33], a method based on the Discrete Logarithm problem over the points on an elliptic curve (EC). Since that time, ECC has received considerable attention from mathematicians around the world, and no significant breakthroughs have been made in determining weaknesses in the algorithm [32,40,41]. Although critics are still skeptical as to the reliability of this method, several ECC encryption techniques have been developed recently. The fact that the problem appears so difficult to crack means that key sizes can be reduced in size considerably, even exponentially [29,33], especially when compared to the key size used by other cryptosystems. ECC became an alternative to RSA, one of the most popular public key methods. ECC offers the same level of security as RSA but with much smaller key size [29].

In order to use ECC, an elliptic curve must be defined over a specific finite field. The EC arithmetic can be optimized depending on the type of finite field. The most popular finite fields used in ECC are *Galois Fields*, GF(p) and  $GF(2^n)$  [9,12,28,29]. The following section will give some background on the EC theory followed by a comparison between ECC arithmetic performed in GF(p) and  $GF(2^n)$ . Then, some ECC applications will be introduced to give an idea of how ECC can be used.

## 2.2 Elliptic Curve Theory

Elliptic curves are described by cubic equations, similar to those used in ellipsis calculations. The general form for an elliptic curve equation is:

$$y^2 + axy + by = x^3 + cx^2 + dx + e$$

.

There is also a single element named the *point at infinity* or the *zero point* denoted ' $\varphi$ '. The point at infinity is computed as the sum of any three points on an EC that lie on a straight line. If a point on the EC is added to another point on the curve or to itself, some special

addition rules are applied depending on the finite field being used and also on the type of coordinate system (affine or projective) its applied to.

As mentioned earlier, a finite field is a set of elements that have a finite order (number of elements). There are many ways of representing the elements of the finite field. Some representations may lead to more efficient implementations of the field arithmetic in hardware or in software. The EC arithmetic is more or less complex depending on the finite field where the EC is applied and in which coordinate system the computation is performed. GF(p) and GF(2<sup>n</sup>), in affine and projective coordinates are considered in this research because they are the most used in ECC [9,11,28,29].

## 2.2.1 Elliptic Curves over Finite Field GF(p)

GF(p) is comprised of the set of integers:  $\{0, 1, 2, \ldots, p-2, p-1\}$ . In this field, the basic arithmetic operations are:

- Addition: a+b=r; where:  $r,a,b \in GF(p)$ , r is the remainder of (a+b) divided by p. This is known as addition modulo p.

- Multiplication:  $a \cdot b = s$ ; where  $a,b,s \in GF(p)$ , s is the remainder of ab divided by p. This is known as multiplication modulo p.

- Squaring:  $a^2 = a$ . a = s; where  $a,s \in GF(p)$ , s is the remainder of  $a^2$  divided by p. Squaring can be assumed as multiplication modulo p.

- Inversion: Assume a is a non-zero element in GF(p), the inverse of a modulo p, denoted  $a^{-1}$ , is the unique integer  $c \in GF(p)$ , for which  $a \cdot c = 1$ .

The EC arithmetic over GF(p) is the usual mod p arithmetic. The EC equation in GF(p) is:  $y^2 = x^3 + ax + b$ ; where p > 3,  $4a^3 + 27b^2 \ne 0$ , and x, y, a,  $b \in GF(p)$ .

The special addition rules in this field are the following:

$$\varphi = -\varphi$$

$$(x, y) + \varphi = (x, y)$$

$$(x, y) + (x, -y) = \varphi$$

#### 2.2.1.1 Affine Coordinates

The addition of two different points on the EC in affine coordinates is computed as:

$$(x_1, y_1) + (x_2, y_2) = (x_3, y_3)$$

; where  $x_1 \neq x_2$

$\lambda = (y_2 - y_1)/(x_2 - x_1)$

$x_3 = \lambda^2 - x_1 - x_2$

$y_3 = \lambda(x_1 - x_3) - y_1$

The addition of a point to itself (doubling a point) is computed as:

$$(x_1, y_1) + (x_1, y_1) = (x_3, y_3)$$

; where  $x_1 \neq 0$

$\lambda = (3(x_1)^2 + a)/(2y_1)$

$x_3 = \lambda^2 - 2x_1$

$y_3 = \lambda(x_1 - x_3) - y_1$

We assume in this work that the squaring calculation is equivalent to a multiplication. Thus, to add two different points in GF(p) we need: six additions, one inversion, and three multiplication operations. To double a point we require: four additions, one inversion, and four multiplications.

# 2.2.1.2 Projective Coordinates

The projective coordinates are used to almost eliminate the need for performing inversion [11,28]. For elliptic curve defined over GF(p), the normal elliptic point (x,y) is projected to (X,Y,Z), where  $x=X/Z^2$ , and  $y=Y/Z^3$  [11]. This transformation between affine and projective coordinates is performed only twice: at the beginning and at the end.

The point addition of P+Q in projective coordinates is computed as:

$$P = (X_1, Y_1, Z_1); Q = (X_2, Y_2, Z_2); P+Q = (X_3, Y_3, Z_3); where P ≠ ±Q$$

$(x, y) = (X/Z^2, Y/Z^3) → (X, Y, Z)$

$\lambda_1 = X_1 Z_2^2$

$\lambda_2 = X_2 Z_1^2$

$\lambda_3 = \lambda_1 - \lambda_2$

$\lambda_4 = Y_1 Z_2^3$

$\lambda_5 = Y_2 Z_1^3$

$\lambda_6 = \lambda_4 - \lambda_5$

$\lambda_7 = \lambda_1 + \lambda_2$

$\lambda_8 = \lambda_4 + \lambda_5$

$Z_3 = Z_1 Z_2 \lambda_3$

$X_3 = \lambda_6^2 - \lambda_7 \lambda_3^2$

$\lambda_9 = \lambda_7 \lambda_3^2 - 2X_3$

$Y_3 = (\lambda_9 \lambda_6 - \lambda_8 \lambda_3^3)/2$

The doubling of a point (P+P) in projective coordinates is computed as:

$$P = (X_{1}, Y_{1}, Z_{1}); P+P = (X_{3}, Y_{3}, Z_{3})$$

$$(x, y) = (X/Z^{2}, Y/Z^{3}) \Rightarrow (X, Y, Z)$$

$$\lambda_{1} = 3X_{1}^{2} + aZ_{1}^{4}$$

$$Z_{3} = 2Y_{1}Z_{1}$$

$$\lambda_{2} = 4X_{1}Y_{1}^{2}$$

$$X_{3} = \lambda_{1}^{2} - 2\lambda_{2}$$

$$\lambda_{3} = 8Y_{1}^{4}$$

$$\lambda_{4} = \lambda_{2} - X_{3}$$

$$Y_{3} = \lambda_{1}\lambda_{4} - X_{3}$$

The squaring calculation in GF(p) is very similar to the multiplication computation. The number of multiplication processes for adding two points is found to be *sixteen*, while the number of operations for doubling a point is found to be only *ten*.

#### 2.2.2 Elliptic Curves over Finite Field GF(2<sup>n</sup>)

GF(2<sup>n</sup>) is called a *characteristic two* field or a binary finite field. It can be viewed as a vector space of dimension n over the field GF(2) that consists of the elements 0 and 1. That is, there exist n elements  $x_0$ ,  $x_1$ ,  $x_2$ , ...,  $x_{n-1}$  in  $GF(2^n)$  such that each element  $x \in GF(2^n)$  can be uniquely written in the form:  $x = a_0 x_0 + a_1 x_1 \dots + a_{n-1} x_{n-1}$ ; where  $a_i \in GF(2)$ . Such a set  $\{x_0, x_1, x_2, \dots, x_{n-1}\}$  is called the *basis* of  $GF(2^n)$  over GF(2). Given such a basis, a field element x can be represented as the bit string  $(a_0 \ a_1 \dots a_{n-1})$ . Addition of field elements is performed by bit-wise XOR-ing their vector representations. The complexity of multiplication depends on the selected basis. There are many different basis of  $GF(2^n)$  over GF(2). Some basis lead to more efficient software or hardware implementations of the arithmetic in  $GF(2^n)$  than others. The most popular basis are the polynomial (or standard) and the normal basis.

The EC equation over  $GF(2^n)$  is:  $y^2 + xy = x^3 + ax^2 + b$ ; where  $x, y, a, b \in GF(2^n)$  and  $b \ne 0$ . The addition rules in this field are as the following:

$$\varphi + \varphi = \varphi$$

$$(x, y) + \varphi = (x, y)$$

$$(x, y) + (x, x+y) = \varphi$$

#### 2.2.2.1 Affine Coordinates

The affine coordinates addition of two different points on the EC is computed as:

$$(x_1, y_1) + (x_2, y_2) = (x_3, y_3)$$

; where  $x_1 \neq x_2$

$\lambda = (y_2 + y_1)/(x_2 + x_1)$

$x_3 = \lambda^2 + \lambda + x_1 + x_2 + a$

$y_3 = \lambda(x_1 + x_3) + x_3 + y_1$

The affine coordinates addition of a point to itself (doubling a point) is computed as:

$$(x_1, y_1) + (x_1, y_1) = (x_3, y_3)$$

; where  $x_1 \neq 0$

$\lambda = x_1 + (y_1)/(x_1)$

$x_3 = \lambda^2 + \lambda + a$

$y_3 = (x_1)^2 + (\lambda + 1) x_3$

To add two different points in  $GF(2^n)$  we need: nine additions, one inversion, one squaring, and two multiplication operations. To double a point we require: five additions, one inversion, two squarings, and two multiplications.

## 2.2.2.2 Projective Coordinates

Calculating the inverse is the most expensive operation. Designs replace the inversion by several multiplication operations by representing the elliptic curve points as projective coordinate points [11,28,30,32]. To almost eliminate the need for performing inversion in  $GF(2^k)$ , its coordinates (x,y) are to be projected to (X,Y,Z), where  $x=X/Z^2$ , and  $y=Y/Z^3$ . The elliptic curve equation in this system is:  $Y^2 + XYZ = X^3 + a X^2Z^2 + b Z^6$  [11].

The point doubling of an elliptic curve point (P+P) in projective coordinates is computed as:

$$P = (X_{1}, Y_{1}, Z_{1}); P+P = (X_{3}, Y_{3}, Z_{3})$$

$$Z_{3} = X_{1}Z_{1}^{2}$$

$$X_{3} = (X_{1} + bZ_{1}^{2})^{4}$$

$$\lambda = Z_{3} + X_{1}^{2} + Y_{1}Z_{1}$$

$$Y_{3} = X_{1}^{4}Z_{3} + \lambda X_{3}$$

The point addition of two elliptic curve points (P+Q) is computed as:

$$P = (X_1, Y_1, Z_1); Q = (X_2, Y_2, Z_2); P+Q = (X_3, Y_3, Z_3); where P ≠ ±Q$$

$(x, y) = (X/Z^2, Y/Z^3) → (X, Y, Z)$

$\lambda_1 = X_1 Z_2^2$

$\lambda_2 = X_2 Z_1^2$

$\lambda_3 = \lambda_1 + \lambda_2$

$\lambda_4 = Y_1 Z_2^3$

$\lambda_5 = Y_2 Z_1^3$

$\lambda_6 = \lambda_4 + \lambda_5$

$\lambda_7 = Z_1 \lambda_3$

$\lambda_8 = \lambda_6 X_2 + \lambda_7 Y_2$

$Z_3 = \lambda_7 Z_2$

$\lambda_9 = \lambda_6 + Z_3$

$X_3 = a Z_3^2 + \lambda_6 \lambda_9 + \lambda_3^3$

$Y_3 = \lambda_9 X_3 + \lambda_8 \lambda_7^2$

The number of multiplication processes for adding two points is found to be *twenty*, while it is found to be *ten* for doubling a point.

# 2.2.3 Comparing Arithmetic Complexity on GF(p) and GF(2<sup>n</sup>)

The number of operations for affine coordinates addition of two different points is found to be basically the same (in GF(p) and GF( $2^n$ )), as shown in Table 2.1. The computation of ' $\lambda$ ' requires one inversion and one multiplication. Computing ' $x_3$ ' needs only one squaring. The value of ' $y_3$ ' is obtained with one multiplication. The number of operations in both fields is identical: one inversion, one squaring, and two multiplications, neglecting the addition, subtraction, and multiplication by small numbers [11,28].

| Point operations | Operations in GF(p) | Operations in GF(2 <sup>n</sup> ) |

|------------------|---------------------|-----------------------------------|

| Point addition   | 1 Inversion         | 1 Inversion                       |

|                  | 3 Multiplications   | 3 Multiplications                 |

| Point doubling   | 1 Inversion         | 1 Inversion                       |

|                  | 4 Multiplications   | 4 Multiplications                 |

Table 2.1 Comparing GF(p) and GF(2<sup>n</sup>) number of lengthy point operations in affine coordinates

Point doubling on affine coordinates requires the computation of ' $\lambda$ ', which in GF(p) requires an inversion, a multiplication, and a squaring of  $x_I$ , while it needs an inversion and a multiplication in GF(2<sup>n</sup>). Calculating ' $x_3$ ' in both fields requires the same operation of squaring lambda. Computing ' $y_3$ ' in GF(p) requires only one multiplication, while it needs a multiplication and a squaring in GF(2<sup>n</sup>). The number of operations is found to be the same in both fields: one inversion, two squarings, and two multiplications [11,28].

Considering projective coordinates (Table 2.2), the number of multiplication processes for adding two points in GF(p) is found to be sixteen, while it is found to be twenty in  $GF(2^n)$ . The number of multiplication calculations for doubling a point is found to be ten in both GF(p) and  $GF(2^n)$ . This shows that GF(p) projective coordinates consumes four less number of multiplications than  $GF(2^n)$ , however, comparison of the number of operations is not accurate because operations in GF(p) require different time than  $GF(2^n)$ . Computations in GF(p) require lengthy time due to the delay of propagating the carry, which  $GF(2^n)$  does not have.

| Point operations | <b>Operations in GF(p)</b> | Operations in GF(2 <sup>n</sup> ) |

|------------------|----------------------------|-----------------------------------|

| Point addition   | 16 Multiplications         | 20 Multiplications                |

| Point doubling   | 10 Multiplications         | 10 Multiplications                |

Table 2.2 Comparing GF(p) and GF(2<sup>n</sup>) number of lengthy point operations in projective coordinates

# 2.2.4 The Elliptic Curve Discrete Logarithm Problem

The elliptic curve discrete logarithm problem is the fundamental mathematical property that supports elliptic curves cryptography. The problem can be clarified by considering E as an elliptic curve and P and Q as points on E; the discrete logarithm problem consists in *finding an integer k such that kP=Q*, if such an integer exists. Figuring the integer k is considered a very hard problem especially if the numbers are large [11]. On the other hand, if integer k and the EC point P are known, computing the other EC point Q is possible. The ECC algorithm used for calculating k (scalar multiplication of k by P,

which is equivalent to add P to itself k times) from P is the binary method, since it is known to be efficient and practical to implement [11,12,29,32]. The binary method algorithm is:

```

Define n: number of bits in k; k_i: the i<sup>th</sup> bit of k

Input: P (a point on the elliptic curve).

Output: Q = kP (another point on the elliptic curve).

1. if k_{n-1} = 1, then Q := P else Q := 0;

2. for i = n-2 down to 0;

3. Q := Q+Q;

4. if k_i = 1 then Q := Q+P;

5. return Q;

```

The binary method algorithm scans the binary representation of k and doubles the point Q n-times. Whenever, a particular bit of k is found to be one, an extra operation is needed. This extra operation is Q+P.

# 2.2.5 Comparing Arithmetic Complexity of Affine and Projective Coordinates

The basic ECC operation consists in computing the point kP from P. Lets use the binary algorithm presented in Section 2.2.4. The number of binary bits of integer k is n, which indicates the exact number of point doublings but not point additions. Assume that the bits of k are half ones and half zeros (an average estimation for comparison reasons). The EC arithmetic operations required are n point doublings and n/2 point additions. The total number of multiplications and inversions for both GF(p) and  $GF(2^n)$  are listed in Table 2.3. If the time to compute l.5n inversions and l.5n multiplications is less than l.8n GF(p) multiplications or l.5n multiplications, then the system based affine coordinates is faster than the one based on projective coordinates. In other words, if one inversion is calculated in less than approximately nine multiplications, then the affine coordinate arithmetic is more appropriate to use than the projective coordinates.

In any case, even with projective coordinates, the inverse computation is still needed at the end of the computation to convert back to affine coordinates and cannot be eliminated completely [1,2,11], which justifies the need to research the alternatives for the design of inverse operation in hardware.

| Finite              | Affine Coordinates Operations              | Projective Coordinates operations |  |

|---------------------|--------------------------------------------|-----------------------------------|--|

| Field               | <i>n</i> doublings & $n/2$ point additions |                                   |  |

| GF(p)               | 1.5n Inversions &                          | 18n Multiplications               |  |

| GF(2 <sup>n</sup> ) | 5.5n Multiplications                       | 20n Multiplications               |  |

Table 2.3 Comparing the affine and projective coordinates

## 2.3 Elliptic Curve Cryptography Applications

As described earlier (Section 2.2.4), it is easy to calculate the point kP from P. However, it is very hard to determine the value of k knowing the two points: kP and P. This property leads to several algorithms for cryptography [29,32]. Some of these techniques will be introduced in the following subsections.

# 2.3.1 Elliptic Curve Diffie-Hellman Key Exchange Method

Secret key cryptosystems are normally used for encryption/decryption purposes, because it is faster than public key cryptosystems. Secret key cryptosystems require a secret key to be agreed upon before the cryptographic process starts. This agreement can be performed by the elliptic curve Diffie-Hellman [29] key exchange method as described by the following example.

Suppose that users A and B want to agree upon a secret key, which will be used for secret key cryptography. Users A and B choose a finite field, GF(p) for example, and an elliptic curve 'E' defined over this field. They also take a randomly chosen point P=(x,y) lying on the elliptic curve E; we refer to P as the *base point* of the cryptosystem. The finite field, the elliptic curve, and the base point are all publicly known.

User A then randomly chooses a large integer  $a \in GF(p)$  and keeps a secret. User A now computes the point aP which will lie on E. User B does the same: B randomly chooses a large integer b and computes bP. Both A and B make aP and bP publicly known. These are their public keys. The secret key that A and B use to encrypt messages sent to each other is abP, which both A and B can compute. User A knows a and bP, and so can

find abP. Whereas, B knows b and aP, and so can find abP. The security of this system lies in the fact that a third party C, for example, knows only aP and bP, and unless C can solve the elliptic curve discrete logarithm problem there is no efficient way to break the encryption.

# 2.3.2 Elliptic Curve Encryption/Decryption

There are many ways to apply elliptic curves for encryption/decryption purposes [29]. A simple method is presented here to give the flavor of elliptic curve encryption/decryption techniques. Assume working with GF(p) finite field and an elliptic curve E. The users randomly chose a base point  $P_{base}$ , lying on the elliptic curve E. The plaintext (the original message to be encrypted) is coded into an elliptic curve point  $P_m$ . Each user selects a private key 'n' and compute his public key  $P = nP_{base}$ . For example, user A's private key is  $n_A$  and his public key is  $P_A = n_A P_{base}$ .

For any one to encrypt and send the message point  $P_m$  to user A, he/she needs to choose a random integer k and generate the ciphertext  $C_m = \{kP_{base}, P_m + kP_A\}$ . The ciphertext pair of points uses A's public key, where only user A can decrypt the plaintext using his private key.

To decrypt the ciphertext  $C_m$ , the first point in the pair of  $C_m$ ,  $kP_{base}$ , is multiplied by A's private key to get the point:  $n_A(kP_{base})$ . Then this point is subtracted from the second point of  $C_m$ , the result will be the plaintext point  $P_m$ . The decryption operations are:

$$(P_m + kP_A)$$

-  $n_A(kP_{base}) = P_m + k(n_AP_{base})$  -  $n_A(kP_{base}) = P_m$

## 2.3.3 Elliptic Curve Digital Signature Algorithm (ECDSA)

The process of ECDSA [29] is composed of three main steps: key generation, signature generation and signature verification. Each step is described as follows:

#### 2.3.3.1 ECDSA key generation

Each user of the scheme does the following:

- 1. Select an elliptic curve E over a finite field, say GF(p). The number of points on E should be divisible by a large prime n.

- 2. Select a point  $P = (x,y) \in GF(p)$  of order n.

- 3. Select a random integer d in the range [1, n-1].

- 4. Compute dP = Q.

- 5. The user's public key is (*Q*, *n*, *P*, *E*); the user's private key is *d*.

### 2.3.3.2 ECDSA signature generation

To sign a message, m, the user does the following:

- 1. Select a random integer k in the range [1, n-1].

- 2. Compute  $kP = (x_1, y_1)$ , and set  $x_1 \mod n = r$ . If r is zero then go back to step 1. In other words, if r = 0 then the signing equation will not involve the private key d.

- 3. Compute  $k^{-1} mod n$ .

- 4. Compute  $s = k^{-1}(h(m) + dr) \mod n$ , where h is the hash value obtained from a suitable hash function.

- 5. If s=0 go to step 1. This because if s is zero then  $s^{-1} \mod n$  does not exist and we would not be able to verify the signature.

- 6. The signature to be included in the message m is the pair of integers (s, r).

#### 2.3.3.3 ECDSA signature verification

To verify the signature (r, s) on the message m, the following should be done:

- 1. Obtain an authentic copy of the public key (Q, n, P, E).

- 2. Verify that r and s are integers in the range [1, n-1].

- 3. Compute  $w = s^{-1} \mod n$  and h(m).

- 4. Compute  $u_1 = h(m).w \mod n$  and  $u_2 = r.w \mod n$ .

- 5. Compute  $u_2Q + u_1P = (x_0, y_0)$  and  $v = x_0 \mod n$ .

- 6. Accept the signature if and only if r = v.

In the above ECDSA algorithms, each user generates their own elliptic curve E, along with a base point P. However, this means that the public key sizes become quite large. If, instead, the users agree upon a fixed curve E and base point P, as system parameters, then each user needs only to define the point Q, which is then all that is included in the public key.

# 3 SCALABLE HARDWARE ARCHITECTURE FOR GF(p) ALMOST MONTGOMERY MODULAR INVERSE COMPUTATION

#### 3.1 Introduction

Modular inversion is often performed by algorithms based on the Extended Euclidean algorithm [11]. Several inversion hardware attempts are described in the literature [16-18,20-25]. Most of the research [17,18,20-25] proposed hardware designs for inversion in Galois Fields  $GF(2^n)$ . Several [17,18,21-25] are based upon parallelism of data flow in an array structure. The inversion in  $GF(2^n)$  is fast due to the elimination of the carry propagation delay in  $GF(2^n)$  calculations. However, the area used in parallel organizations are very large, of order  $O(n^2)$ . Hasan in [20] proposed a design of the inversion algorithm that is smaller in area and still keeps a fair speed. He performed a word-by-word computation of the numbers instead of computing the whole numbers in parallel. Since we focus on GF(p), the designs proposed in [17,18, 21-25] have no direct link to this work. Takagi in [16], proposed an inverse algorithm for hardware with a redundant binary representation. Each number is represented by digits in the set  $\{0,1,-1\}$ . Redundant representation is used to reduce the carry propagation delay problem. However, it requires more area. It also needs data transformation that is usually expensive.

The Montgomery modular inverse algorithm suitable for our research is presented in [1]. The algorithm requires two main operations: a Montgomery product and an *almost Montgomery inverse* (AlmMonInv) operation. This Chapter is directed towards the implementation of the AlmMonInv. The Montgomery product is beyond the scope of this work and scalable Montgomery multipliers, such as the ones proposed in [6-8] can generate it.

Two AlmMonInv designs are presented in this Chapter, namely a fixed precision design and a scalable hardware design. The fixed precision design is fully parallel and processes full precision numbers at every clock cycle. The scalable hardware, however, divides the numbers in words where each word is processed in a clock cycle. We show that the scalable hardware is more appropriate for cryptographic applications.

## 3.2 Montgomery Inverse Algorithms

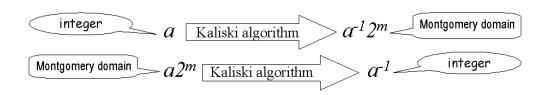

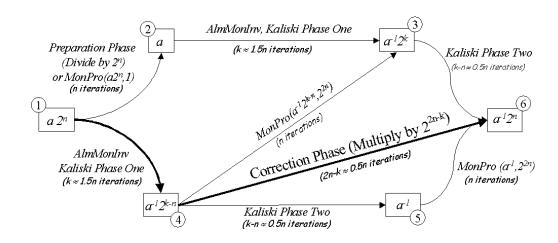

Two Montgomery modular inverse studies are found in the literature [1,2]. Both modify a technique proposed by Kaliski in 1995 [3], to make it more suitable and faster for cryptography using Montgomery's idea. Kaliski method, derived from the extended Euclidean algorithm [3], basically takes an integer a, and produces x, where  $x=a^{-1}2^m \mod p$ . If a is an integer, the algorithm will calculate the inverse of a, but represented in Montgomery domain, as shown in Figure 3.1. When the number a is already in Montgomery domain, the application of Kaliski's routine will not give the needed Montgomery inverse result. Thus, some extra arithmetic operations are required to get it. Kaliski method is summarized next. It is followed by a brief explanation of two modifications to Kaliski's work to make it compute the Montgomery inverse and to make it faster.

Figure 3.1 Types of input/output numbers for Kaliski algorithm

#### 3.2.1 Kaliski Algorithm

Kaliski algorithm [1,3] is shown below and it is divided in two phases. Phase one, also called almost Montgomery inverse (AlmMonInv) in this work, takes the inputs a and p and give outputs r and k; where  $r = a^{-1}2^k \mod p$ , and n < k < 2n (n is the actual number of bits of the modulus p). Phase two takes the outputs of phase one as its inputs, and gives the final result of Kaliski algorithm:  $x = a^{-1}2^m \mod p$ . Note that in both phases the integers: a and a are within the range [1,p-1]. Kaliski's two phases are outlined as follows:

```

Phase One: Almost Montgomery Inverse, AlmMonInv(a)

```

```

Input: a and p; where a is in the range [1,p-1].

Output: r and k; where r = a^{-1}2^k \mod p, n < k < 2n, n = number of bits of p

u = p; v = a; r = 0; and s = 1

1.

2.

k = 0

3.

while (v > 0)

4.

if u is even then u = u/2; s = 2s

5.

else if v is even then v = v/2; r = 2r

else if u > v then u = (u - v)/2; r = r + s; s = 2s

6.

7.

else v = (v - u)/2: s = s + r: r = 2r

k = k + 1

8.

9.

if r \ge p then r = r - p

10.

return r = p - r

Phase Two

Input: r,p,k \& m; where r \& k from phase one, \& m \ge n (m=Montgomery constant)

Output: x; where x = a^{-1}2^m \mod p

for i = 1 to k - m do

12.

if r is even then r = r/2

13.

else r = (r + p)/2

14.

return x = r

```

# 3.2.2 Modifications to Kaliski Algorithm

T. Kobayashi and H. Morita in 1999 [2], proposed techniques for modular inversion to make it more than five times faster than the original Kaliski routine. They gained speed from the comparison of the values of u and v (step 6), they compare the most significant word only. Their way to achieve more speed consisted in combining the multiplication and the shifting operations. Long numbers were divided into words. They modified the AlmMonInv algorithm by performing several matrix multiplications, instead of the simple multiplications by two. The modification was targeted toward software implementations.

In July 2000, Savas and Koç [1] proposed to replace phase two of Kaliski's algorithm with a Montgomery multiplication, which resulted in a faster process. They also presented a complete Montgomery modular inverse algorithm by adding extra Montgomery multiplication operations. These extra multiplications are performed after the AlmMonInv. The Montgomery inverse computation algorithm in [1] is outlined below:

### Montgomery Inverse Algorithm

```

Input: a2^m \pmod{p}, p, n, m, and R^2 \mod p

Output: x = a^{-1}2^m \mod p, where x is in the range [1,p-1].

1. (r,k) = \text{AlmMonInv}(a2^m); where r = a^{-1}2^{-m}2^k \mod p, and n \le k \le m+n

2. If n \le k \le m then

2.1 r = \text{MonPro}(r,R^2) = (a^{-1}2^{-m}2^k)(a^{2m})(2^{-m}) = a^{-1}2^k \mod p

2.2 k = k+m > m

3. r = \text{MonPro}(r,R^2) = (a^{-1}2^{-m}2^k)(2^{2m})(2^{-m}) = a^{-1}2^k \mod p

4. r = \text{MonPro}(r, 2^{2m-k}) = (a^{-1}2^k)(a^{2m-k})(2^{-m}) = a^{-1}2^m \mod p

5. Return x = r; where x = a^{-1}2^m \mod p

```

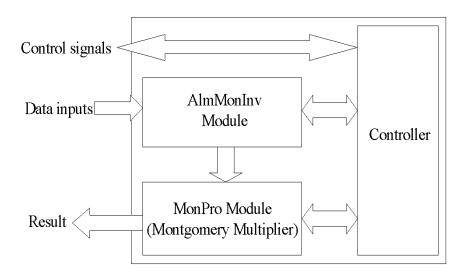

The input parameters are the integers  $aR \mod p$  (residue representation of a), n, m and p (the modulus, a prime number of size n-bits,  $m \ge n$ ), and  $R^2 \mod p$  (a pre-computed integer based on the Montgomery radix,  $R = 2^m$  [1]). The two main procedures used in the Montgomery inverse algorithm are the *Montgomery product* (MonPro) and the *almost Montgomery inverse* (AlmMonInv) [1], modeled in hardware as shown in Figure 3.2. Our contribution consists in the implementation of the almost Montgomery inverse procedure in hardware. The MonPro is beyond the scope of this work.

Figure 3.2 The complete Montgomery modular inverse hardware

#### 3.3 The Fixed Precision Design

This section discuses a fixed precision hardware design. We present some hardware issues applied to the algorithm to compute the almost Montgomery inverse (AlmMonInv) subroutine, which is basically phase-one of Kaliski's algorithm.

## 3.3.1 Hardware Issues Applied to the Algorithm

When observed from hardware point-of-view, the AlmMonInv algorithm contains operations that are easily mapped to hardware features. For example, one-bit shifting the binary representation of number u to the right (ShiftR(u,1)) is equivalent to perform division by two, or one-bit shifting s to the left (ShiftL(s,1)) is equal to do multiplication by two. Checking for a number to be even or odd requires a test of the least significant bit (LSB). If it is found to be zero the number is even, otherwise the number is odd. The comparison of two numbers to see which one is bigger is performed after subtracting one from the other. If the subtraction result is positive (the borrow-bit is zero) the first number is bigger, or vice-versa. Such hardware mapping is shown in the hardware algorithm below:

The Fixed Precision Hardware AlmMonInv Algorithm (FHW-Alg)

```

Registers: u, v, r, s, and p (all five registers are to hold n-bits).

Input:

a \in [1, p - 1], p = modulus.

result \in [1, p-1] and k; where result = a^{-1}2^k \pmod{p} and n < k < 2n

Output:

u = p; v = a; r = 0; s = 1; k = 0

1.

if (u_0 = 0) then \{ u = ShiftR(u, 1) ; s = ShiftL(s, 1) \}; go to step 7

if (v_0 = 0) then: { v = ShiftR(v, 1) ; r = ShiftL(r, 1)}; go to step 7

S1 = Subtract(u, v); S2 = Subtract(v, u); A1 = Add(r, s)

5.

if (S1_{borrow} = 0) then \{u = ShiftR(S1,1)\}; r = A1; s = ShiftL(s,1)\}; go to step 7

s = A1; v = ShiftR(S2,1); r = ShiftL(r,1)

6.

7.

k = k + 1

if (v \neq 0) go to step 2

S1 = Subtract(p, r), S2 = Subtract(2p, r)

10. if (S1_{borrow} = 0) then {return result = S1}; else {return result = S2}

```

Consider step 6 of AlmMonInv, if u>v then the subtraction (u-v) takes place, otherwise, the subtraction (v-u) is calculated. In the worst case, two subtraction operations are performed, because the comparison of u and v may be accomplished through subtraction of u and v anyway. These two subtractions can be done in parallel (two subtraction modules) as shown in step 4 of FHW-Alg. The same case applies to step 9 and step 10 of AlmMonInv, both subtractions may be performed in parallel.

All actual integers are represented by n-bit vectors, such as  $u = (u_{n-1}, u_{n-2}, ....., u_2, u_1, u_0)$ . The modulus is loaded into register u at step 1, then, register u is modified along with the algorithm. The modulus is essential at steps 9 and 10 (FHW-Alg) and for this reason, it is stored in a special register named p. The value of r cannot equal p except when q equals infinity. Thus, the result of AlmMonInv equals either p if q is greater than p, or p-q when q is less than p, as described in step 10 of FHW-Alg.

# 3.3.2 The Fixed Precision Hardware Design

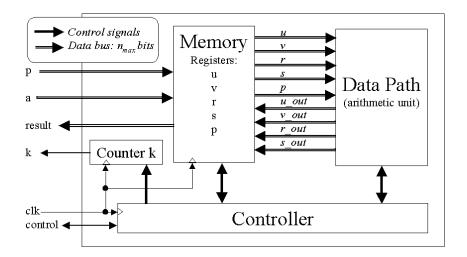

The fixed precision design is made up of a memory unit, a controller, a k-counter, and a data path (arithmetic unit). The block diagram for this hardware design is shown in Figure 3.3. All data buses are  $n_{max}$  bits wide ( $n_{max}$  is the maximum number of bits the hardware can handle). The memory unit is made of five registers u, v, r, s and p to hold  $n_{max}$  bits each. The memory unit sends out all its content and loads new ones at every clock cycle, except for register p that does not change during the computation. The data path (DP) takes the memory unit outputs and gives back the computed data to be stored through buses:  $u\_out$ ,  $v\_out$ ,  $r\_out$ , and  $s\_out$ . For example, in step 3 of FHW-Alg, only v and r are modified. However, the DP provides the data to all four buses. Buses  $v\_out$  and  $r\_out$  are found to be modifications of v and r, while  $u\_out$  and  $s\_out$  are just the same u and s fed back.

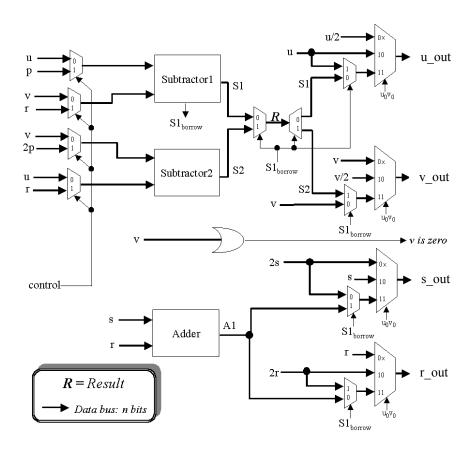

The DP performs the required computation depending on the LSBs of u and v, as clarified by FHW-Alg. It contains several multiplexers to route and shift the data buses to perform steps 2, 3, 5, 6 and 10, as shown in Figure 3.4. It consists of an adder and two subtractors to perform steps 4 and 9. The counter unit performs step 7 of FHW-Alg. All the components in the design are directed and synchronized by the controller.

Figure 3.3 The block diagram of implementing the FHW-Alg

Figure 3.4 The fixed precision hardware data path

#### 3.4 The Scalable Design

# 3.4.1 Why scalable design?

Application specific hardware architectures are usually designed to deal with a specific maximum number of bits, 512-bits for example. If this number of bits is to be increased, even by one, the complete hardware needs to be replaced. In addition to that, if the design is implemented for a large number of bits, the hardware is huge and its' longest path usually is impractical. It will cause the hardware to run at a very low clock frequency unless architectural changes are applied. These issues motivated the search for a scalable hardware similar to what is proposed by Tenca and Koç in their *Scalable Architecture for Montgomery Multiplication* [6].

The scalable architecture solves the previous problems with the following three hardware features. First, the design's longest path should be short and independent of the operands' length. Second, it is designed in such a way that it fits in restricted hardware regions (flexible area). Finally, it can handle the computation of numbers in a repetitive way up to a certain limit usually imposed by the size of the memory in the design. If the number of bits in the data exceeds the memory size, the memory unit is replaced while the scalable computing unit is not changed.

# 3.4.2 Scalable Hardware Issues Applied to the Algorithm

Differently from what happens in the fixed precision hardware design, the scalable hardware has multi-precision operators for addition, subtraction and comparison. The subtraction used for comparison (u > v), is performed on a word-by-word basis until all the actual data words are processed, then, the subtractor borrow out bit is used to decide on the result. Also, depending on the subtraction completion, variable r or s has to be shifted. All variables, u, v, r and s, need to remain as is until the subtraction processes complete, and the borrow out bit appears. Such a constraint forced the use of three more variables: x, y

and z; where x = u - v, y = v - u and z = r + s. These variables are stored in extra registers as outlined in the scalable algorithm.

The Scalable Hardware Algorithm (SHW-Alg)

```

Registers: u, v, r, s, x, y, z & p (all eight registers are to hold n_{max} bits).

a \in [1, p-1], p = modulus.

Output: result \in [1,p-1] & k; where result = a^{-1}2^k \pmod{p} & n < k < 2n, (n < n_{max})

u = p; v = a; r = 0; s = 1; x = 0; y = 0; z = 0; k = 0

if (u_0 = 0) then \{ u = ShiftR(u,1) ; s = ShiftL(s,1) \}; go to step 7

if (v_0 = 0) then \{v = ShiftR(v, 1); r = ShiftL(r, 1)\}; go to step 7

3.

x = Subtract(u, v); y = Subtract(v, u); z = Add(r, s)

if (x_{borrow}=0)then \{u=ShiftR(x,1); r=z; s=ShiftL(s,1)\}; goto step 7

5.

s = z; v = ShiftR(y,1); r = ShiftL(r,1)

7.

k := k + 1

8.

if (v \neq 0) go to step 2

x = Subtract(p, r); y = Subtract(2p, r)

10. if (x_{borrow} = 0) then {return result = x}; else {return result = y}

```

All operations (addition, subtraction, and shifting) of the scalable hardware algorithm are multi-precision computations. In other words, the numbers are utilized in each operation on a word-by-word basis until the entire number is processed.

# 3.4.3 The Scalable Hardware Design

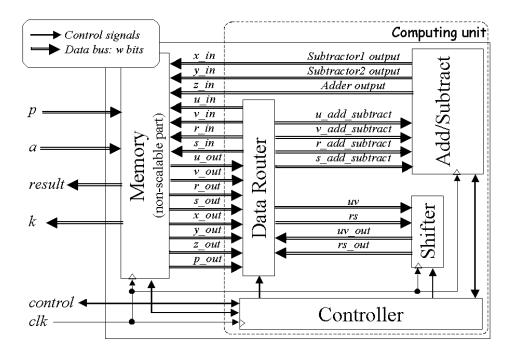

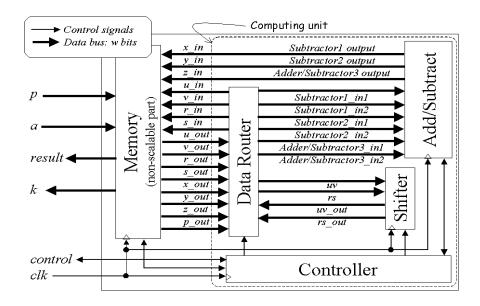

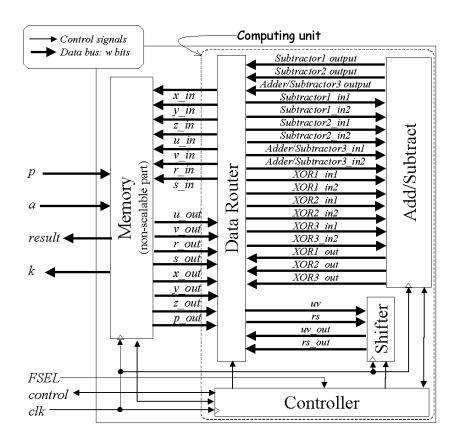

The scalable hardware design is built of two main parts, a memory unit and a computing unit. The memory unit is not scalable because it has a limited storage defined by the value  $n_{max}$ . The data values of a and p are first loaded in the memory unit. Then, the computing unit read/write (modify) the data using a word size of w bits. The computing unit is completely scalable. It is designed to handle w bits every clock cycle. The computing unit does not know the total number of bits,  $n_{max}$ , the memory is holding. It computes until the controller indicates that all operands words were processed. Note that the actual numbers used may have much less than  $n_{max}$  bits.

The block diagram for the scalable hardware is shown in Figure 3.5. The memory unit is connected to the computing unit components. The computing unit is made of four hardware blocks, add/subtract block, shifter block, data router block, and the controller. All these computing unit blocks are briefly clarified after describing the non-scalable memory

unit. The memory unit contains a counter to compute k (step 7 of SHW-Alg) and eight first-in-first-out (FIFO) registers used to store the algorithm's variables. All registers, u, v, r, s, x, y, z and p, are limited to hold at most  $n_{max}$  bits. Each FIFO register has its own reset signal generated by the controller. They have counters ( $n_{counter}$  bits each) to keep track of n (the number of bits actually used by the application).

Figure 3.5 The scalable hardware overall block diagram

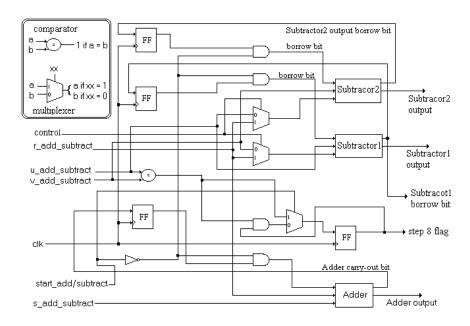

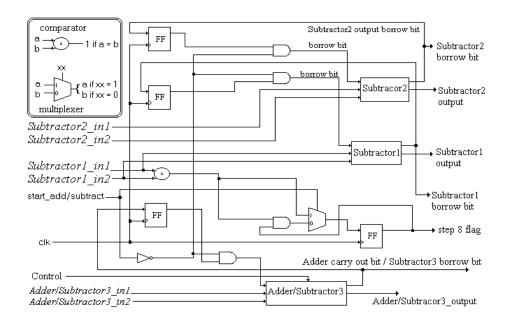

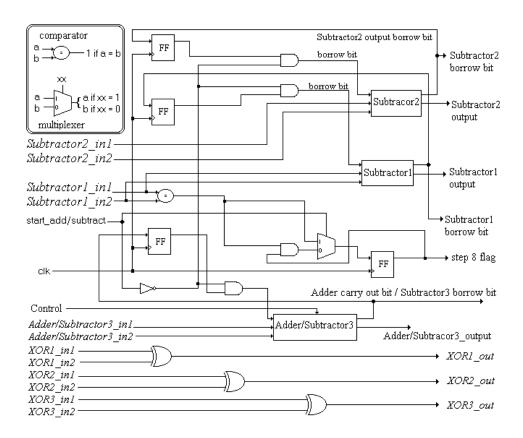

The add/subtract unit is built of an adder, two subtractors, four flip-flops, three multiplexers, a comparator, and logic gates, connected as shown in Figure 3.6. This unit performs one of two operations, either to calculate step 4 of SHW-Alg: x = u-v, y = v-u, and z = r+s, or to calculate step 9: x = p-r and y = 2p-r. Three flip-flops are used to hold the intermediate carry-bit of the adder and borrow-bits of the two subtractors to implement the multi-precision operations. The fourth flip-flop is used to store a flag that keeps track of the comparison between u and v. This flag is used to perform step 8 of SHW-Alg. The

first subtractor borrow out bit is connected to the controller through a signal that is useful only at the end of the each multi-precision addition/subtraction operation. It will affect the flow of the operation to choose either step 5 or step 6 of SHW-Alg. It is also essential in choosing the final result observed in step 10 of SHW-Alg.

Figure 3.6 The scalable add/subtract unit

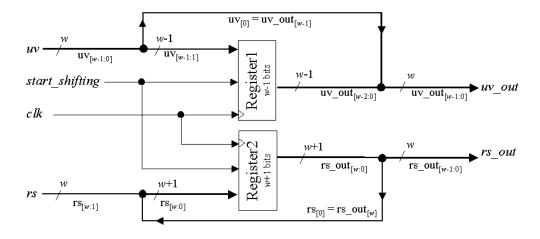

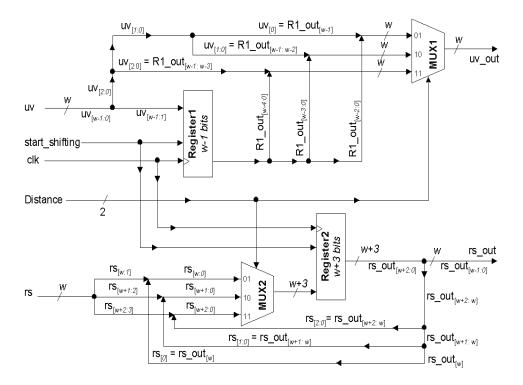

The shifter is made of two registers with special mapping of some data bits, as shown in Figure 3.7. Two types of shifting are needed in the hardware algorithm, shifting an operand (u or v) through the uv bus one bit to the right, and shifting another operand (r or s) through the rs bus one bit to the left. The input buses uv and rs are w bits noted in figure 3.7 as vectors  $uv_{[w-l:0]}$  and  $rs_{[w-l:0]}$ , respectively. Shifting u or v is performed through Register1, which is of size w-l bits. For each word, all the bits of uv are stored in Register1 except the least significant bit  $(uv_{[0]})$ , it is read out immediately as the most significant bit (MSB) of the output bus  $uv\_out$   $(uv\_out_{[w-l]})$ . The MSB of the output of Register2 (vector  $rs\_out_{[w:0]}$ , bit  $rs\_out_{[w]}$ ) is mapped as least significant bit (LSB) of the input of Regester2, to perform the shifting to the left.

Figure 3.7 The scalable hardware shifter

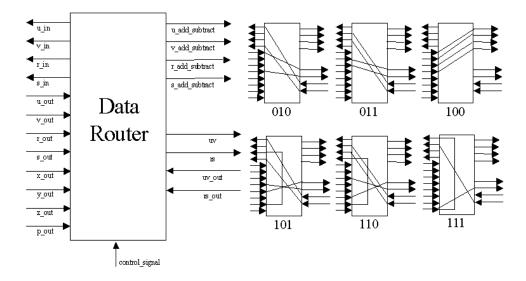

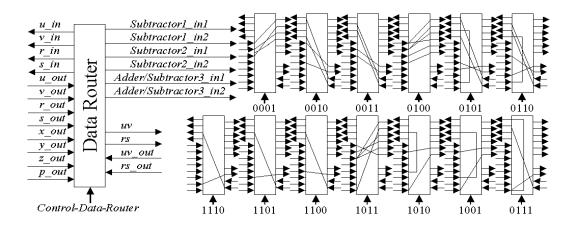

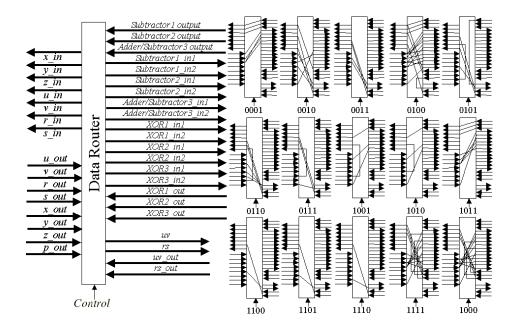

The data router is made of ten multiplexers to connect the data going out of the memory unit to the inputs of the add/subtract unit or shifter. It also directs the shifted data values to go to their required locations in the memory unit. The possible configurations of the data router are shown in Figure 3.8.

Figure 3.8 The data router configurations

The controller is the unit that coordinates the flow of data to guide the hardware computation. Its made of a state machine easily derived from SHW-Alg. The controller does not include counters to avoid any dependency on the number of bits that the system can handle. Such modules are left into the memory block.

# 3.5 Modeling and Analysis

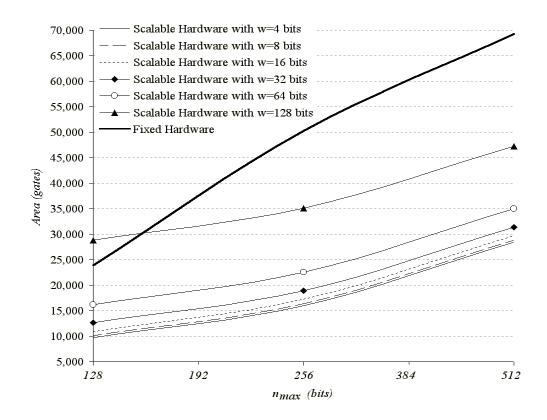

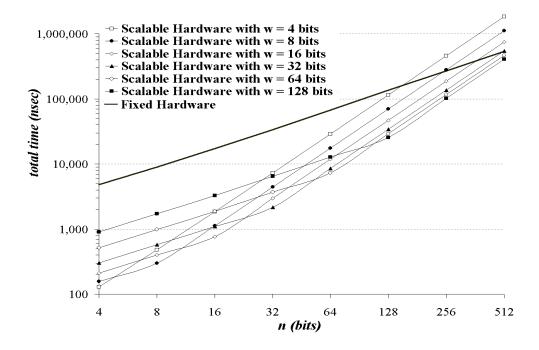

Both designs were modeled and simulated in VHDL. The developed VHDL implementation of the scalable hardware has two main parameters, namely  $n_{max}$  and w. The fixed precision hardware, however, is parameterized by  $n_{max}$  only. Their area and speed are presented in this section. We didn't define a specific architecture for the adders and subtractors used in the design. Thus, the synthesis tool chooses the best option in terms of area from its library of standard cells. The impact of the use of different adders is described in Chapter 4.

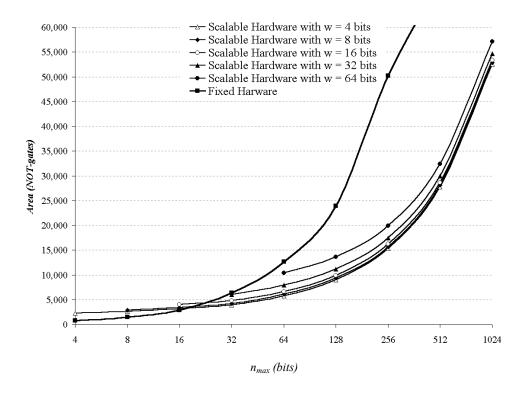

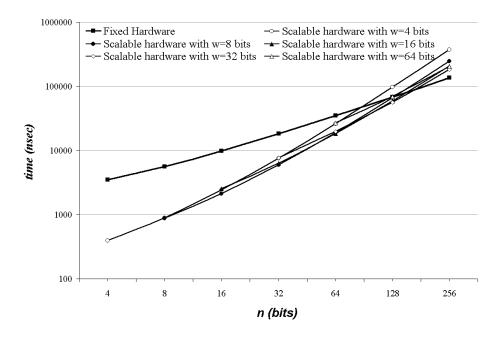

# 3.5.1 Area Comparison